Rev. 1.10

24

November 26, 2019

Rev. 1.10

25

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

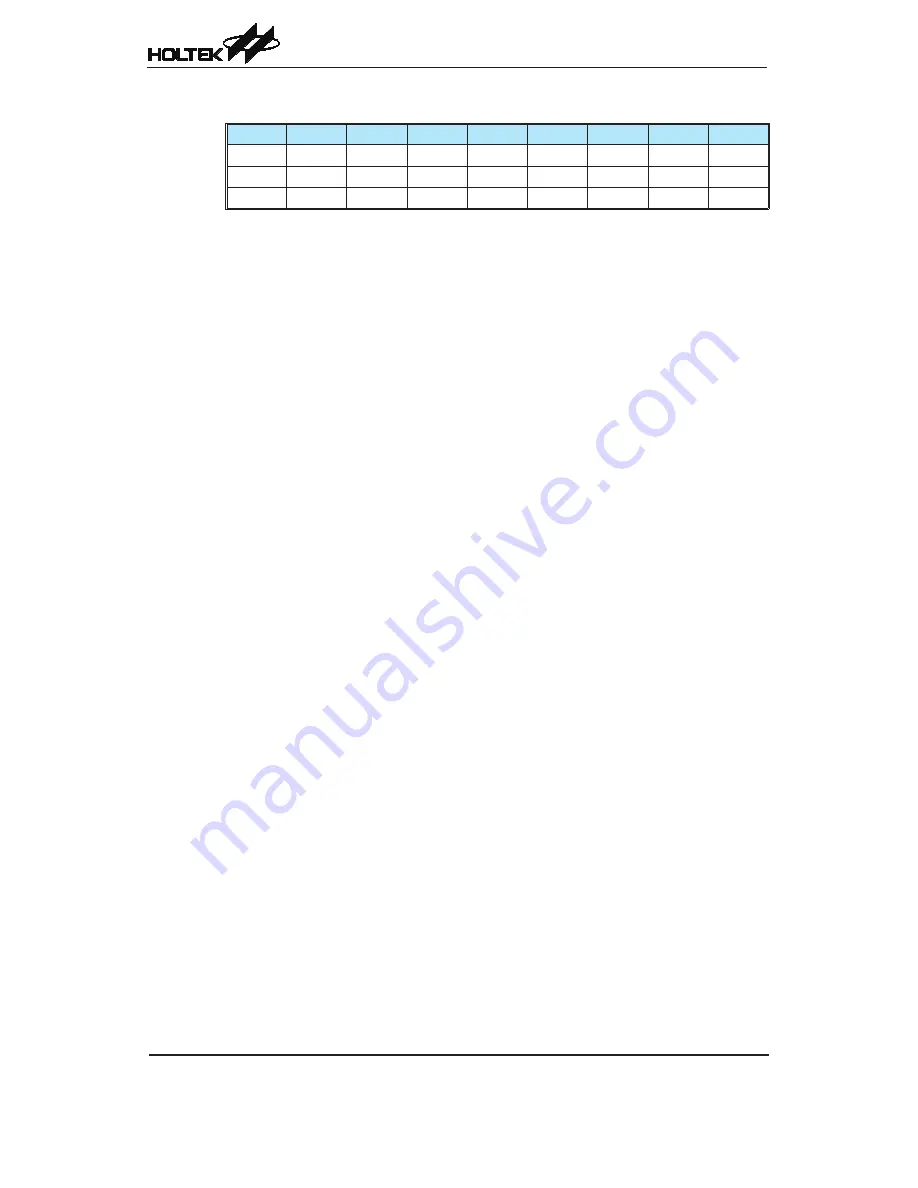

• FRCR Register

Bit

7

6

5

4

3

2

1

0

Name

—

—

—

FSWRST

—

—

—

CLWB

R/W

—

—

—

R/W

—

—

—

R/W

POR

—

—

—

0

—

—

—

0

Bit 7~5

Unimplemented, read as "0"

Bit 4

FSWRST:

Software Reset MCU control bit

Described elsewhere

Bit 3~1

unimplemented, read as "0"

Bit 0

CLWB:

Flash Program memory Write buffer clear control bit

0: do not initiate clear Write Buffer or clear process

1: initiate clear Write Buffer process

This bit is used to control the Flash Program memory clear Write buffer process. It

will be set by software and cleared by hardware.

In Application Program – IAP

Offering users the convenience of Flash Memory multi-programming features, the device not only

provide

s an ISP function, but also an additional IAP function. The convenience of the IAP function

is that it can execute the updated program procedure using its internal firmware, without requiring an

external Program Writer or PC. In addition, the IAP interface can also be any type of communication

protocol, such as UART or SPI, using I/O pins. Designers can assign I/O pins to communicate with

the external memory device, including the updated program. Regarding the internal firmware, the

user can select versions provided by HOLTEK or create their own. The following section illustrates

the procedures regarding how to implement IAP firmware.

Enable Flash Write Control Procedure

The first procedure to implement the IAP firmware is to enable the Flash Write control which

includes the following steps.

•

Write data "110" to the FMOD[2:0] bits in the FCR register to enable the Flash write control bit,

FWEN.

•

Set the BWT bit in the FCR register to "1".

•

The device will start a 1ms counter. The user should write the correct data pattern into the Flash

data registers, namely FD1L~FD3L and FD1H~FD3H, during this period of time.

•

Once the 1ms counter has overflowed or if the written pattern is incorrect, the enable Flash write

control procedure will be invalid and the user should repeat the above procedure.

•

No matter whether the procedure is valid or not, the devices will clear the BWT bit automatically.

•

The enable Flash write pattern data is (00H, 04H, 0DH, 09H, C3H and 40H) and it should be

written into the Flash data registers.

•

Once the Flash write operation is enabled, the user can update the Flash memory using the Flash

control registers.

•

To disable the Flash write procedure, the user can only clear the CFWEN bit in the FCR register.

There is no need to execute the above procedure.