Rev. 1.10

84

November 26, 2019

Rev. 1.10

85

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

I

2

C Registers

There are three control registers associated with the I

2

C bus, SIMC0, SIMC1 and SBSC, one

address register SIMA and one data register, SIMD. The SIMD register, which is shown in the

above SPI section, is used to store the data being transmitted and received on the I

2

C bus. Before

the microcontroller writes data to the I

2

C bus, the actual data to be transmitted must be placed in the

SIMD register. After the data is received from the I

2

C bus, the microcontroller can read it from the

SIMD register. Any transmission or reception of data from the I

2

C bus must be made via the SIMD

register.

Note that the SIMA register also has the name SIMC2 which is used by the SPI function. Bit SIMEN

and bits SIM2~SIM0 in register SIMC0 are used by the I

2

C interface. The I2CDB0 and I2CDB1 in

the SBSC register are used to select the I

2

C debounce time.

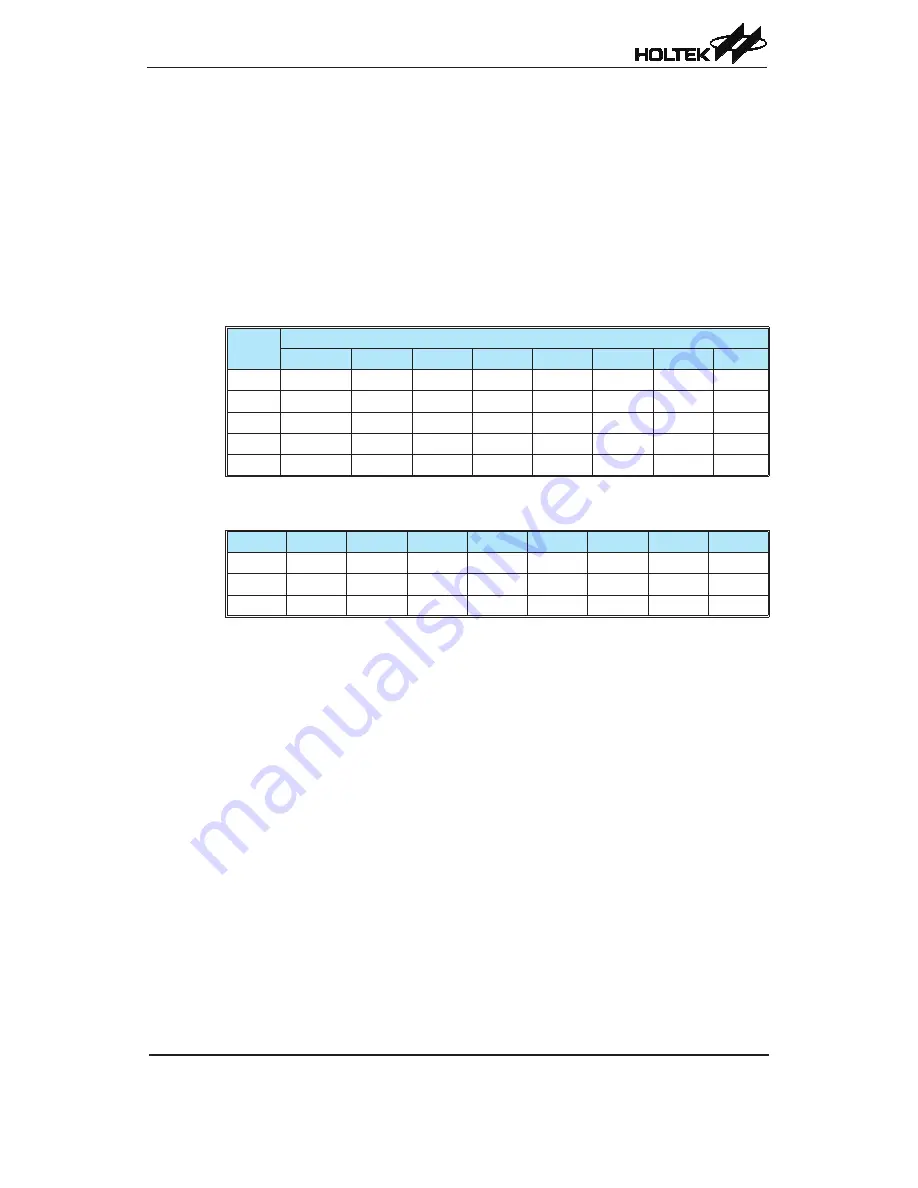

Register

Name

Bit

7

6

5

4

3

2

1

0

SIMC0

SIM2

SIM1

SIM0

PCKEN

PCKP1

PCKP0

SIMEN

—

SIMC1

HCF

HAAS

HBB

HTX

TXAK

SRW

IAMWU

RXAK

SIMD

D7

D6

D5

D4

D3

D2

D1

D0

SIMA

IICA6

IICA5

IICA4

IICA3

IICA2

IICA1

IICA0

D0

SBSC SIM_WCOL

—

I2CDB1

I2CDB0

—

—

—

—

I

2

C Registers List

SIMC0 Register

Bit

7

6

5

4

3

2

1

0

Name

SIM2

SIM1

SIM0

PCKEN

PCKP1

PCKP0

SIMEN

—

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

—

POR

1

1

1

0

0

0

0

—

Bit 7~5

SIM2~SIM0:

SIM Operating Mode Control

000: SPI master mode; SPI clock is f

SYS

/4

001: SPI master mode; SPI clock is f

SYS

/16

010: SPI master mode; SPI clock is f

SYS

/64

011: SPI master mode; SPI clock is

f

LIRC

100: SPI master mode; SPI clock is TM0 CCRP match frequency/2

101: SPI slave mode

110: I

2

C slave mode

111: I/O mode

These bits setup the overall operating mode of the SIM function. As well as selecting

if the I

2

C or SPI function, they are used to control the SPI Master/Slave selection and

the SPI Master clock frequency. The SPI clock is a function of the system clock but

can also be chosen to be sourced from the TM0. If the SPI Slave Mode is selected then

the clock will be supplied by an external Master device.

Bit 4

PCKEN:

PCK Output Pin Control

0: Disable

1: Enable

Bit 3~2

PCKP1, PCKP0:

Select PCK output pin frequency

00: f

SYS

01: f

SYS

/4

10: f

SYS

/8

11: TM0 CCRP match frequency/2