14. Register Descriptions > PCI Capability Registers

162

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

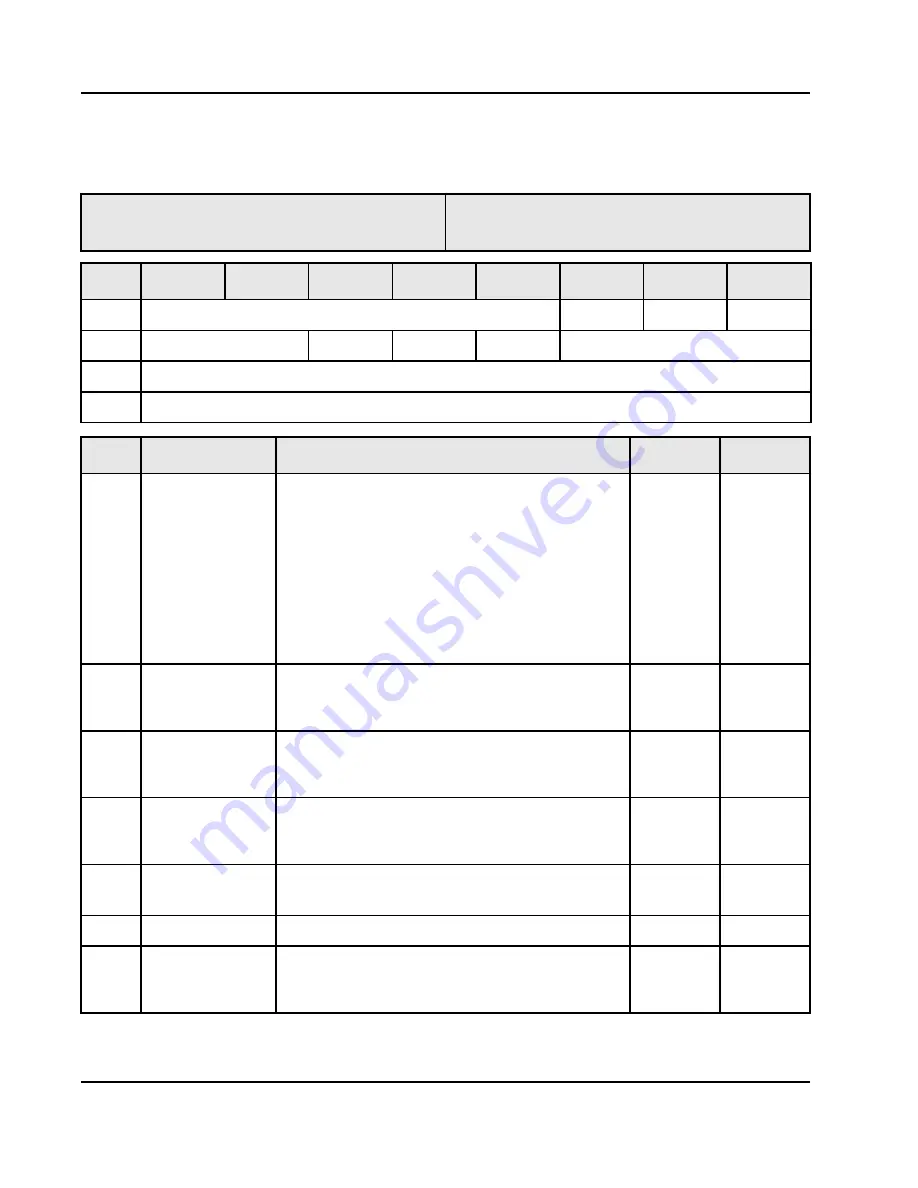

14.5.4

PCI Power Management Capability Register

This register defines bytes 0 to 3 of the power management capability option.

Register name: PCI_PMC

Reset value: 0x7803_C001

Register offset: 0x0A0

Bits

7

6

5

4

3

2

1

0

31:24

PME_SUP

D2_SP

D1_SP

AUX_CUR

23:16

AUX_CUR

DSI

Reserved

PME_CK

PM_VER

15:08

NXT_PTR

07:00

CAP_ID

Bits

Name

Description

Type

Reset value

31:27

PME_SUP

PME Support

This field indicates the power management states from

which the PEB383 device can indicate PME#.

The value reported by this field is based on Serial EEPROM

programming that indicates how auxiliary power is routed to

the PEB383 device in the system.

Given the right power supplies, the PEB383 can assert the

PME# signals in D3

COLD

.

In the absence of Serial EEPROM information, the PEB383

will report PME support for power levels down to D3

HOT

.

RWL

01111

26

D2_SP

D2 Support

This field always returns 0 since the PEB383 does not

support the D2 power management state.

R

0

25

D1_SP

D1 Support

This field always returns 0 since the PEB383 does not

support the D1 power management state.

R

0

24:22

AUX_CUR

Aux Current

This field returns a value 0 indicating the device is self

powered.

R

000

21

DSI

Device Specific Initialization

Hardwired to 0. No special initialization is required.

R

0

20

Reserved

Reserved. It always reads 0.

R

0

19

PME_CK

PME Clock

This field is not applicable to devices with a PCIe Interface.

It always reads 0.

R

0