9. Error Handling > PCIe as Originating Interface

69

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

In the case of an Advisory Non-Fatal Error detection, the following actions are taken by the PEB383:

1.

If the severity of the TLP Error detected in

“PCIe Uncorrectable Error Severity Register”

is

Non-Fatal then:

a. COR_ERR_DTD is set in the

“PCIe Device Control and Status Register”

b. ANFE is set in the

“PCIe Correctable Error Status Register”

2.

And if the ANFE bit is not masked in the

“PCIe Correctable Error Mask Register”

a. TLP Error Status bit is set in the

“PCIe Uncorrectable Error Status Register”

b. If the corresponding TLP Error Mask bit is clear in the

“PCIe Uncorrectable Error Mask

and ERR_PTR is not valid in the

“PCIe Advanced Error Capabilities and Control

, then the TLP header is logged in the

is updated in the

“PCIe Advanced Error Capabilities and Control Register”

.

c. If COR_ERR_EN is set in the

“PCIe Device Control and Status Register”

Correctable error message.

9.2.1

Received Poisoned TLPs

When the bridge receives a poisoned TLP it completes the following while forwarding it to the PCI

Interface:

1.

If the severity of the PTLP in the

“PCIe Uncorrectable Error Severity Register”

is Non-Fatal and

the ANFE Mask bit is clear in

“PCIe Correctable Error Mask Register”

then:

•

A Correctable error message is generated if the COR_ERR_EN bit is set in the

•

ANFE bit is set in the

“PCIe Correctable Error Status Register”

•

COR_ERR_DTD bit is set in the

“PCIe Device Control and Status Register”

•

PTLP bit is set in the

“PCIe Uncorrectable Error Status Register”

•

TLP header is logged in the Header Log register and ERR_PTR is updated if the PTLP Mask

bit in

“PCIe Uncorrectable Error Mask Register”

is clear and the ERR_PTR is not valid

2.

If the severity of the PTLP bit in

“PCIe Uncorrectable Error Severity Register”

is Non-Fatal and

“PCIe Correctable Error Mask Register”

then:

•

No error message is generated

•

COR_ERR_DTD bit is set in the

“PCIe Device Control and Status Register”

•

ANFE bit is set in the

“PCIe Correctable Error Status Register”

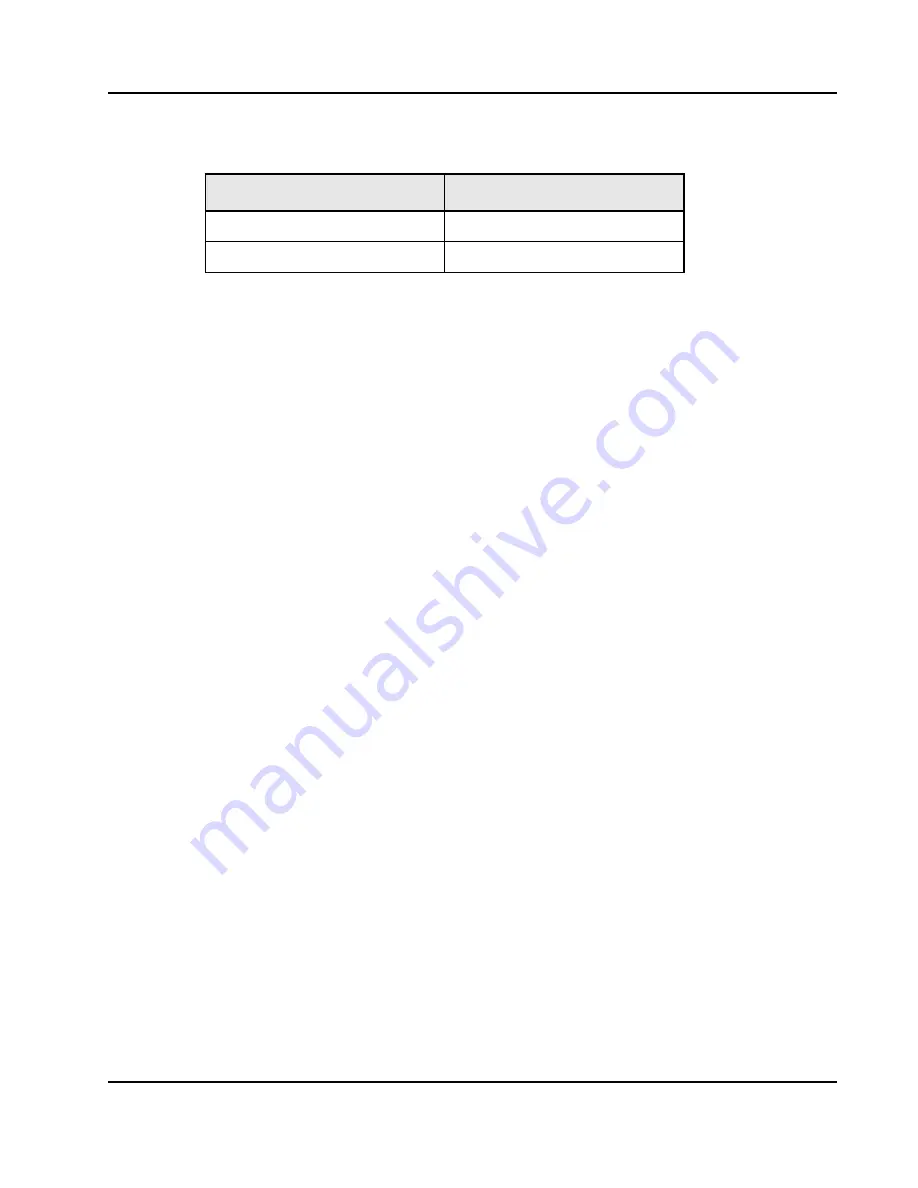

Master-Abort

Unsupported Request

Target-Abort

Completer Abort

Table 14: Bridge Requirements for Transactions Requiring a Completion

(Immediate Response)

Immediate PCI Termination

PCIe Completion Status