> PCIe and SerDes Control and Status Registers

216

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

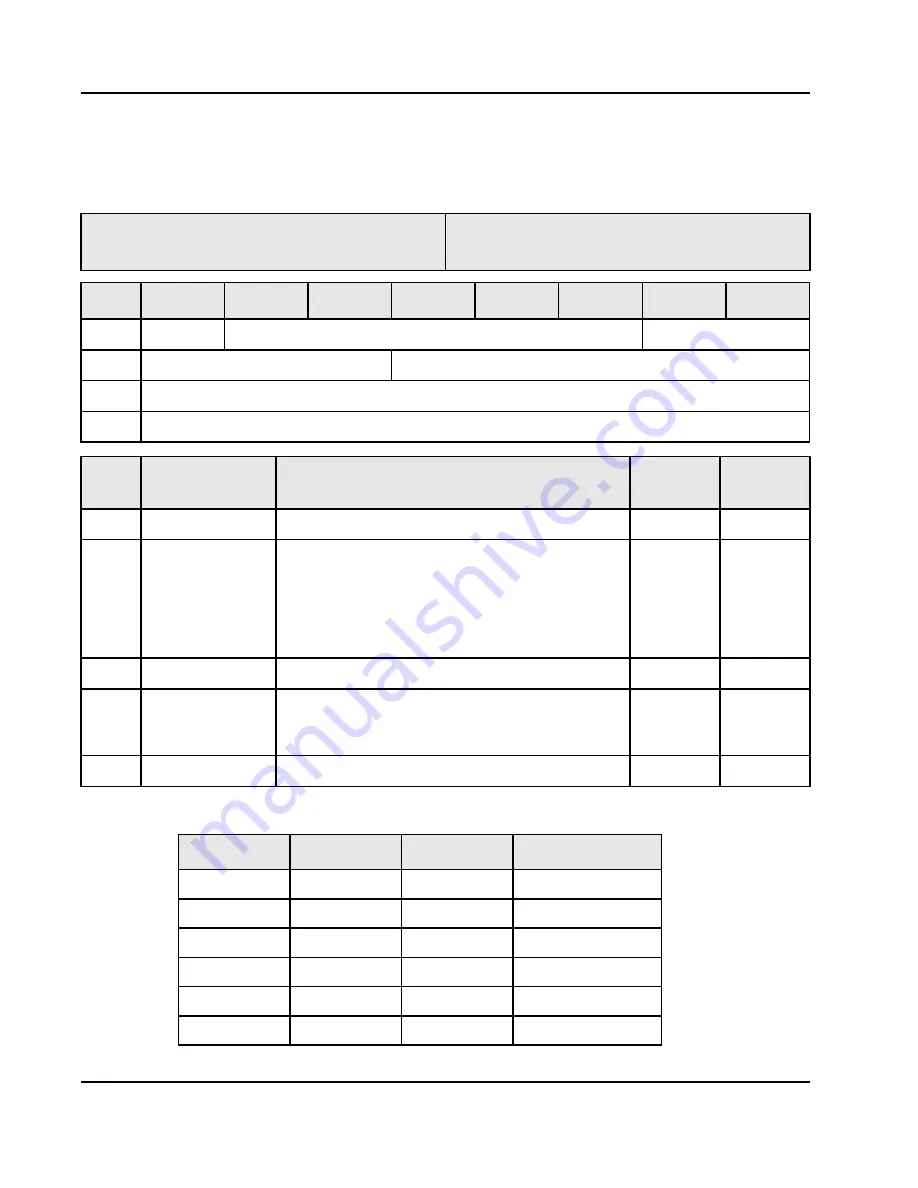

14.9.12

PCIe Control and Level Override Register

The register provides a method for overriding the value of TX_LVL, LOS_LVL, and ACJT_LVL in the

“PCIe Control and Level Status Register”

Register name: PCIE_CTL_OVRD

Reset value: Undefined

Register offset: 0x428

Bits

7

6

5

4

3

2

1

0

31

:

24

OVRD

TX_LVL

LOS_LVL

23

:

16

LOS_LVL

ACJT_LVL

15:08

Reserved

07:00

Reserved

Bits

Name

Description

Type

Reset

Value

31

OVRD

Override all level controls.

R/W

0

30:26

TX_LVL

Fine Resolution setting of Tx signal level.

Equation: Pk-Pk output level (without attenuation) = 1230 x

(48 + tx_lvl/2)/63.5 mV Vdiff-pp

Note: TX_LVL should be set to >= 0x1010 (which results in

an output of 1Vp-p). For more information on available

settings, see

R/W

0x10

25:21

LOS_LVL

Loss of Signal Detector level

R/W

0x10

20:16

ACJT_LVL

AC JTAG Receiver Comparator level

This sets the hysteresis level for AC JTAG. For information

on setting the correct voltage levels, see IEEE 1149.6.

R/W

0x10

15:0

ReservedP

Preserve state on writes.

R/W

Undefined

Table 39: TX_LVL Values

TX_LVL

Value

TX_LVL[0:4]

Vdiff-pp (mV)

0

0x00

5'b00000

929.8

1

0x01

5'b00001

939.4

2

0x02

5'b00010

949.1

3

0x03

5'b00011

958.8

4

0x04

5'b00100

968.5

5

0x05

5'b00101

978.2