XC2200 Derivatives

System Units (Vol. 1 of 2)

Central Processing Unit (CPU)

User’s Manual

4-37

V2.1, 2008-08

CPUSV2_X, V2.2

4.6

Code Addressing

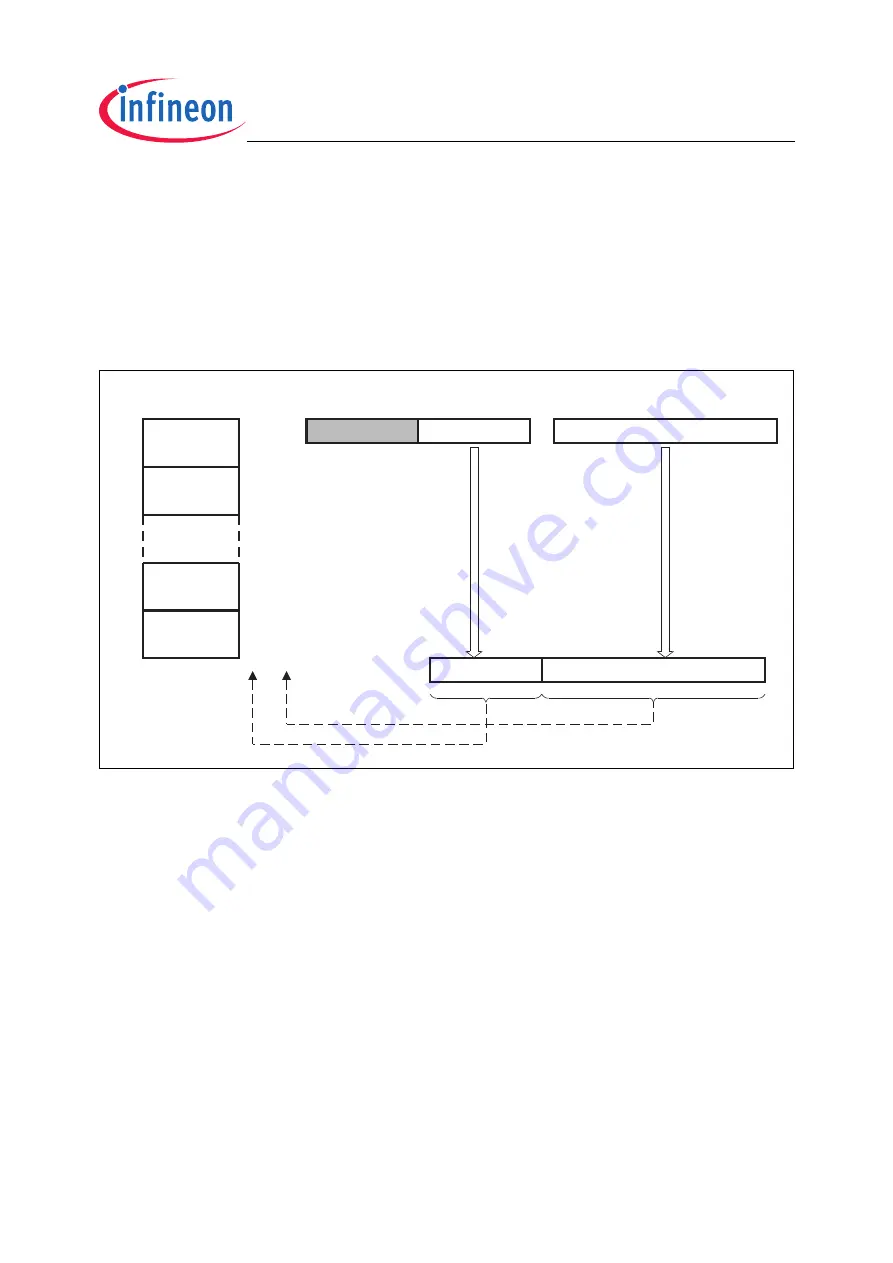

The XC2200 provides a total addressable memory space of 16 Mbytes. This address

space is arranged as 256 segments of 64 Kbytes each. A dedicated 24-bit code address

pointer is used to access the memories for instruction fetches. This pointer has two parts:

an 8-bit code segment pointer CSP and a 16-bit offset pointer called Instruction Pointer

(IP). The concatenation of the CSP and IP results directly in a correct 24-bit physical

memory address.

Figure 4-12 Addressing via the Code Segment and Instruction Pointer

tbd RAS

The Code Segment Pointer CSP

selects the code segment being used at run-time to

access instructions. The lower 8 bits of register CSP select one of up 256 segments of

64 Kbytes each, while the higher 8 bits are reserved for future use. The reset value is

specified by the contents of the VECSEG register (

Note: Register CSP can only be read but cannot be written by data operations.

In segmented memory mode

(default after reset), register CSP is modified either

directly by JMPS and CALLS instructions, or indirectly via the stack by RETS and RETI

instructions.

In non-segmented memory mode

(selected by setting bit SGTDIS in register

CPUCON1), CSP is fixed to the segment of the instruction that disabled segmentation.

Modification by inter-segment CALLs or RETurns is no longer possible.

MCA04920

15

23

0

Memory organized

in segments

255

254

1

0

FF'0000

H

FE'0000

H

01'0000

H

00'0000

H

16

15

0

IP

15

0

CSP

7

8

Segment

Offset