XC2200 Derivatives

System Units (Vol. 1 of 2)

Central Processing Unit (CPU)

User’s Manual

4-59

V2.1, 2008-08

CPUSV2_X, V2.2

Z-Flag:

The Z-flag is normally set to 1 if the result of an ALU operation equals zero,

otherwise it is cleared.

For the addition and subtraction with carry, the Z-flag is only set to 1, if the Z-flag already

contains a 1 and the result of the current ALU operation also equals zero. This

mechanism is provided to support multiple precision calculations.

For Boolean bit operations with only one operand, the Z-flag represents the logical

negation of the previous state of the specified bit. For Boolean bit operations with two

operands, the Z-flag represents the logical NORing of the two specified bits. For the

prioritize ALU operation, the Z-flag indicates whether the second operand was zero.

E-Flag:

End of table flag. The E-flag can be altered by instructions which perform ALU

or data movement operations. The E-flag is cleared by those instructions which cannot

be reasonably used for table search operations. In all other cases, the E-flag value

depends on the value of the source operand to signify whether the end of a search table

is reached or not. If the value of the source operand of an instruction equals the lowest

negative number which is representable by the data format of the corresponding

instruction (8000

H

for the word data type, or 80

H

for the byte data type), the E-flag is set

to 1; otherwise, it is cleared.

General Control Functions (USR0, USR1, BANK, HLDEN)

A few bits in register PSW are dedicated to general control functions. Thus, they are

saved and restored automatically upon task switches and interrupts.

USR0/USR1-Flags:

These bits can be set automatically during the execution of

repeated MAC instructions. These bits can also be used as general flags by an

application.

BANK:

Bitfield BANK selects the currently active register bank (local or global). Bitfield

BANK is updated implicitly by hardware upon entering an interrupt service routine, and

by a RETI instruction. It can be also modified explicitly via software by any instruction

which can write to PSW.

HLDEN:

Setting this bit for the first time activates the selected bus arbitration mode (see

). Bus arbitration can be disabled by temporarily clearing bit HLDEN. In this

case the bus is locked, while the bus arbitration mode remains selected.

Table 4-24

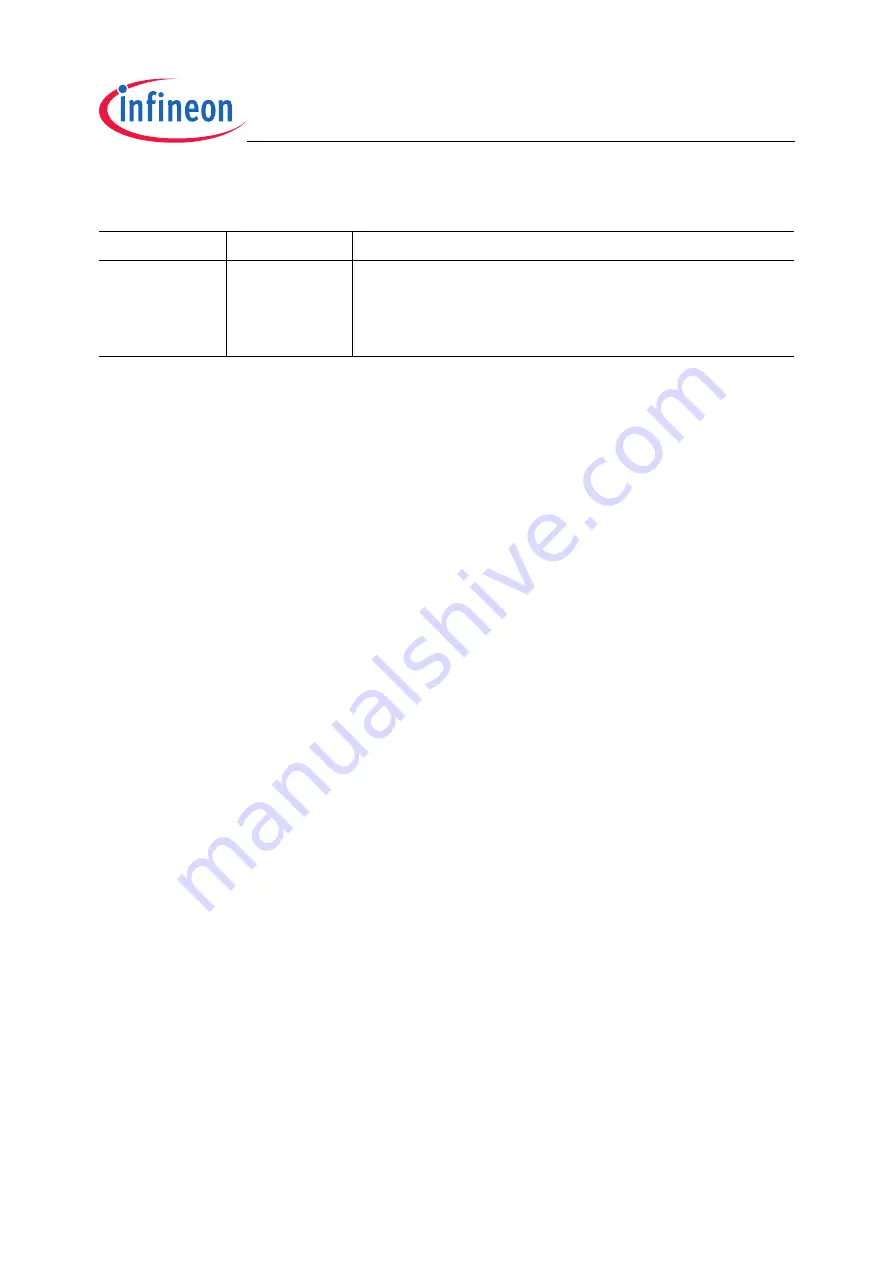

Shift Right Rounding Error Evaluation

C-Flag

V-Flag

Rounding Error Quantity

0

0

1

1

0

1

0

1

No rounding error

0 < Rounding error <

1

/

2

LSB

Rounding error =

1

/

2

LSB

Rounding error >

1

/

2

LSB