XC2200 Derivatives

System Units (Vol. 1 of 2)

Interrupt and Trap Functions

User’s Manual

5-40

V2.1, 2008-08

ICU_X2K, V2.2

5.10

Service Request Latency

The numerous service requests of the XC2200 (requests for interrupt or PEC service)

are generated asynchronously with respect to the execution of the instruction flow.

Therefore, these requests are arbitrated and are inserted into the current instruction

stream. This decouples the service request handling from the currently executed

instruction stream, but also leads to a certain latency.

The request latency is the time from activating a request signal at the interrupt controller

(ITC) until the corresponding instruction reaches the pipeline’s execution stage.

lists the consecutive steps required for this process.

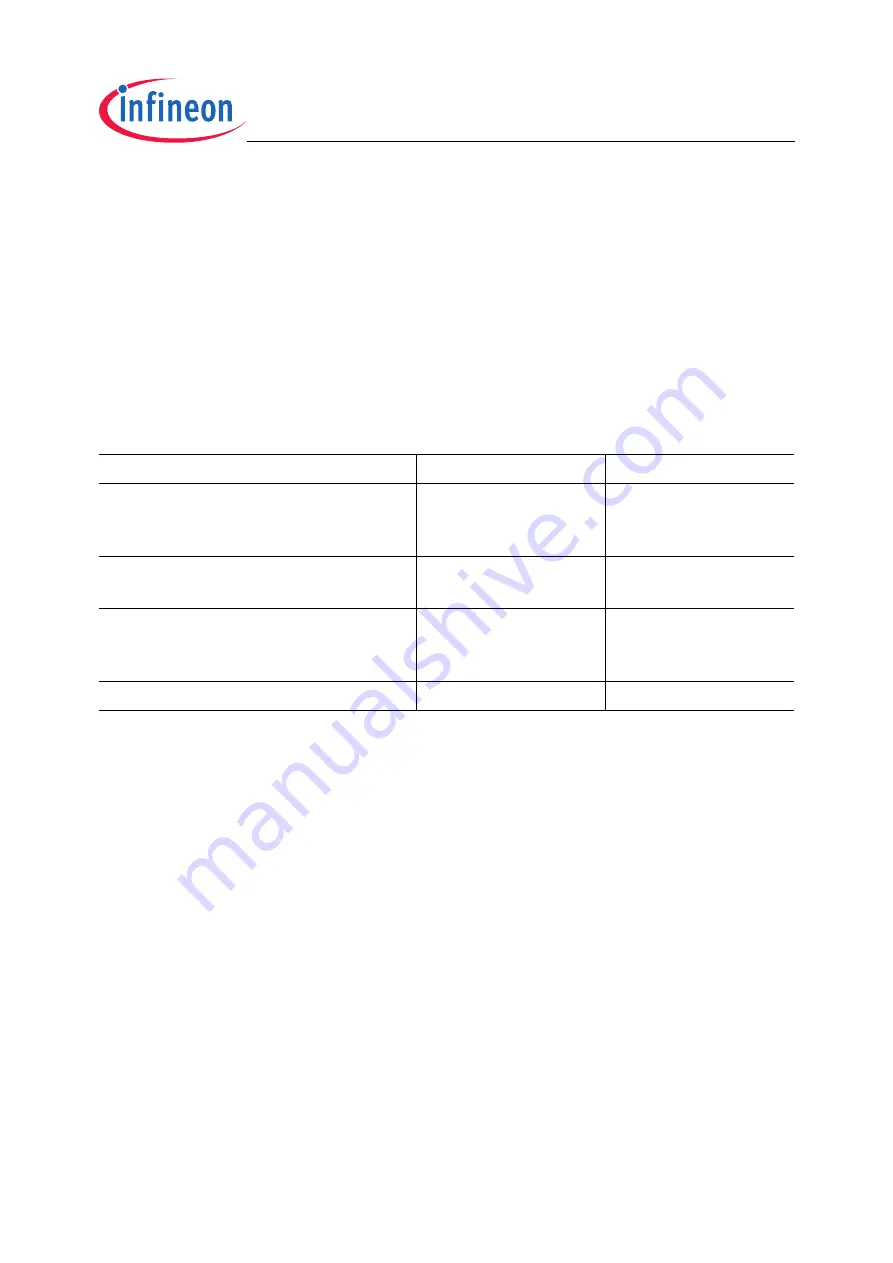

Table 5-13

Steps Contributing to Service Request Latency

Description of Step

Interrupt Response

PEC Response

Request arbitration in 3 stages,

leads to acceptance by the CPU

(see

)

3 cycles

3 cycles

Injection of an internal instruction into

the pipeline’s instruction stream

4 cycles

4 cycles

The first instruction fetched from the

interrupt vector table reaches the

pipeline’s execution stage

4 cycles / 0

1)

1) Can be saved by using the interrupt jump table cache (see

).

- - -

Resulting minimum request latency

11/7 cycles

7 cycles