XC2200 Derivatives

System Units (Vol. 1 of 2)

Interrupt and Trap Functions

User’s Manual

5-18

V2.1, 2008-08

ICU_X2K, V2.2

Interrupt Jump Table Cache

Servicing an interrupt request via the vector table usually incurs two subsequent

branches: an implicit branch to the vector location and an explicit branch to the actual

service routine. The interrupt servicing time can be reduced by the Interrupt Jump Table

Cache (ITC, also called “fast interrupt”). This feature eliminates the second explicit

branch by directly providing the CPU with the service routine’s location.

The ITC provides two 24-bit pointers, so the CPU can directly branch to the respective

service routines. These fast interrupts can be selected for two interrupt sources on

priority levels 15 … 12.

The two pointers are each stored in a pair of interrupt jump table cache registers

(FINTxADDR, FINTxCSP), which store a pointer’s segment and offset along with the

priority level it shall be assigned to (select the same priority that is programmed for the

respective interrupt node).

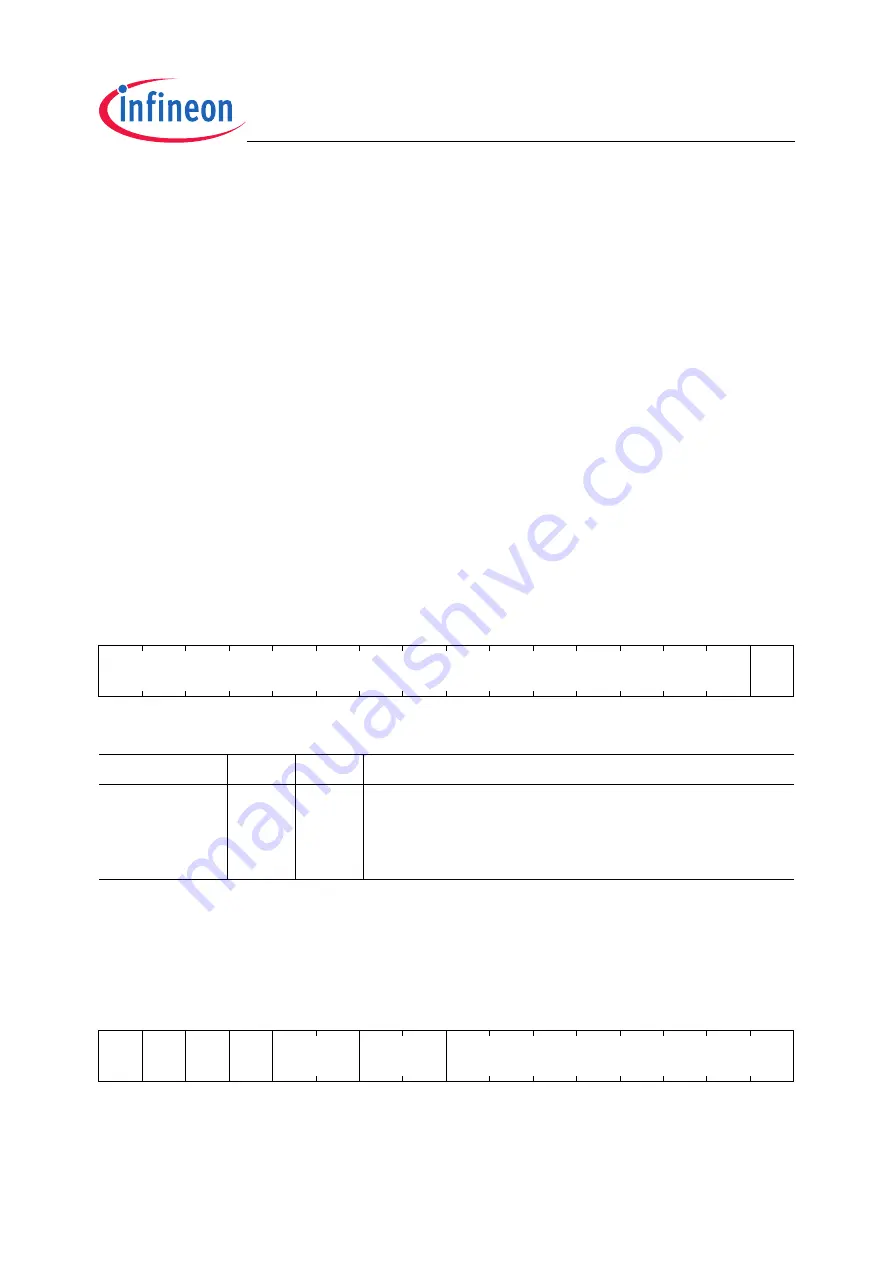

FINT0ADDR

Fast Interrupt Address Reg. 0

XSFR (EC02

H

/--)

Reset Value: 0000

H

FINT1ADDR

Fast Interrupt Address Reg. 1

XSFR (EC06

H

/--)

Reset Value: 0000

H

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ADDR

0

rw

r

Field

Bits

Type

Description

ADDR

[15:1]

rw

Address of Interrupt Service Routine

Specifies address bits 15 … 1 of the 24-bit pointer to

the interrupt service routine. This word offset is

concatenated with FINTxCSP.SEG.

FINT0CSP

Fast Interrupt Control Reg. 0

XSFR (EC00

H

/--)

Reset Value: 0000

H

FINT1CSP

Fast Interrupt Control Reg. 1

XSFR (EC04

H

/--)

Reset Value: 0000

H

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

EN

-

-

GPX

ILVL

GLVL

SEG

rw

-

-

rw

rw

rw

rw