System Integration Module (SIM)

Exception Control

MC68HC908GP32

•

MC68HC08GP32

—

Rev. 6

Technical Data

MOTOROLA

System Integration Module (SIM)

289

processing can resume.

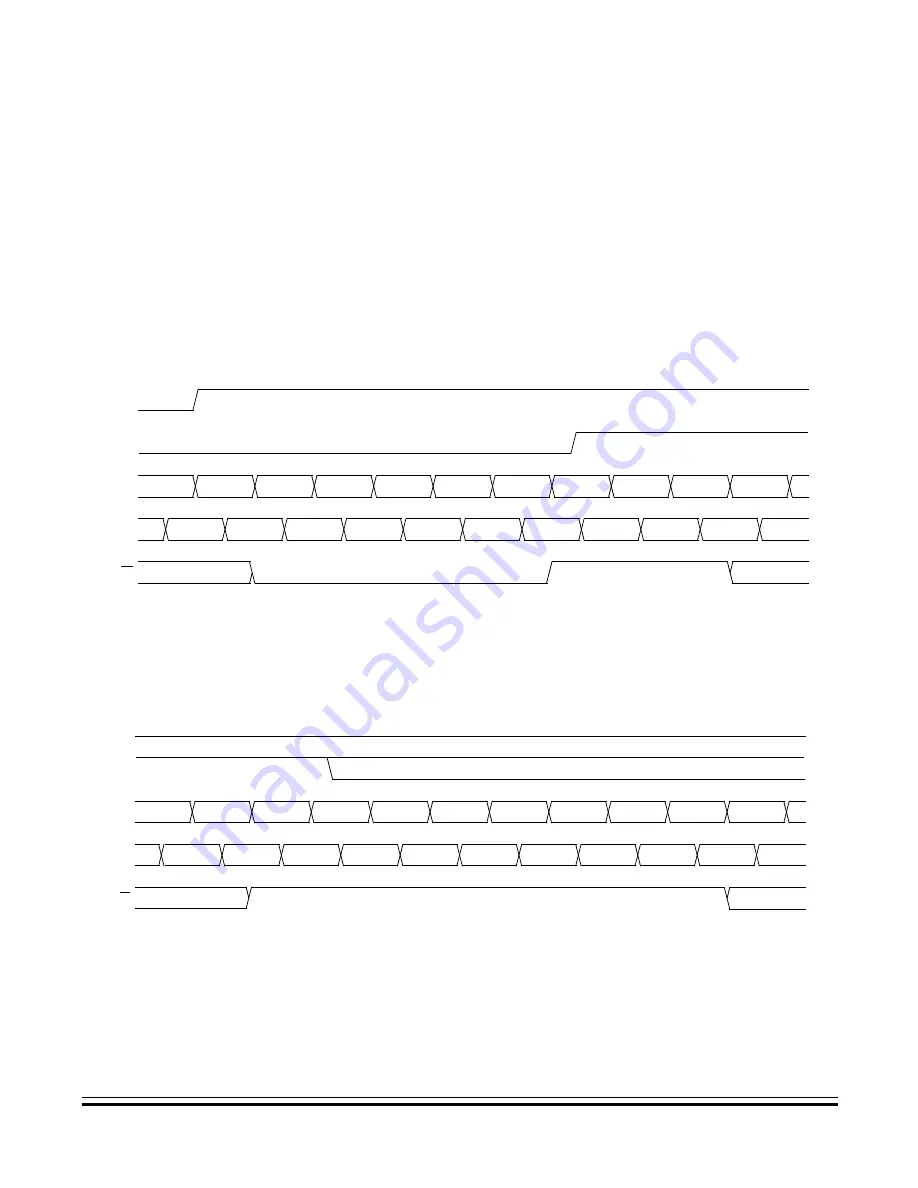

Figure 19-8

shows interrupt entry timing.

Figure 19-9

shows interrupt recovery timing.

Interrupts are latched, and arbitration is performed in the SIM at the start

of interrupt processing. The arbitration result is a constant that the CPU

uses to determine which vector to fetch. Once an interrupt is latched by

the SIM, no other interrupt can take precedence, regardless of priority,

until the latched interrupt is serviced (or the I bit is cleared).

(See

Figure

19-10

.)

Figure 19-8

.

Interrupt Entry Timing

Figure 19-9. Interrupt Recovery Timing

MODULE

IDB

R/W

INTERRUPT

DUMMY

SP

SP – 1

SP – 2

SP – 3

SP – 4

VECT H

VECT L

START ADDR

IAB

DUMMY

PC – 1[7:0] PC – 1[15:8]

X

A

CCR

V DATA H

V DATA L

OPCODE

I BIT

MODULE

IDB

R/W

INTERRUPT

SP – 4

SP – 3

SP – 2

SP – 1

SP

PC

PC + 1

IAB

CCR

A

X

PC – 1 [15:8] PC – 1 [7:0]

OPCODE

OPERAND

I BIT

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..