UG-707

ADV8005 Hardware Reference Manual

8.3.1.

Interrupt Architecture Overview

The following three interrupts are required by the VSP and OSD section:

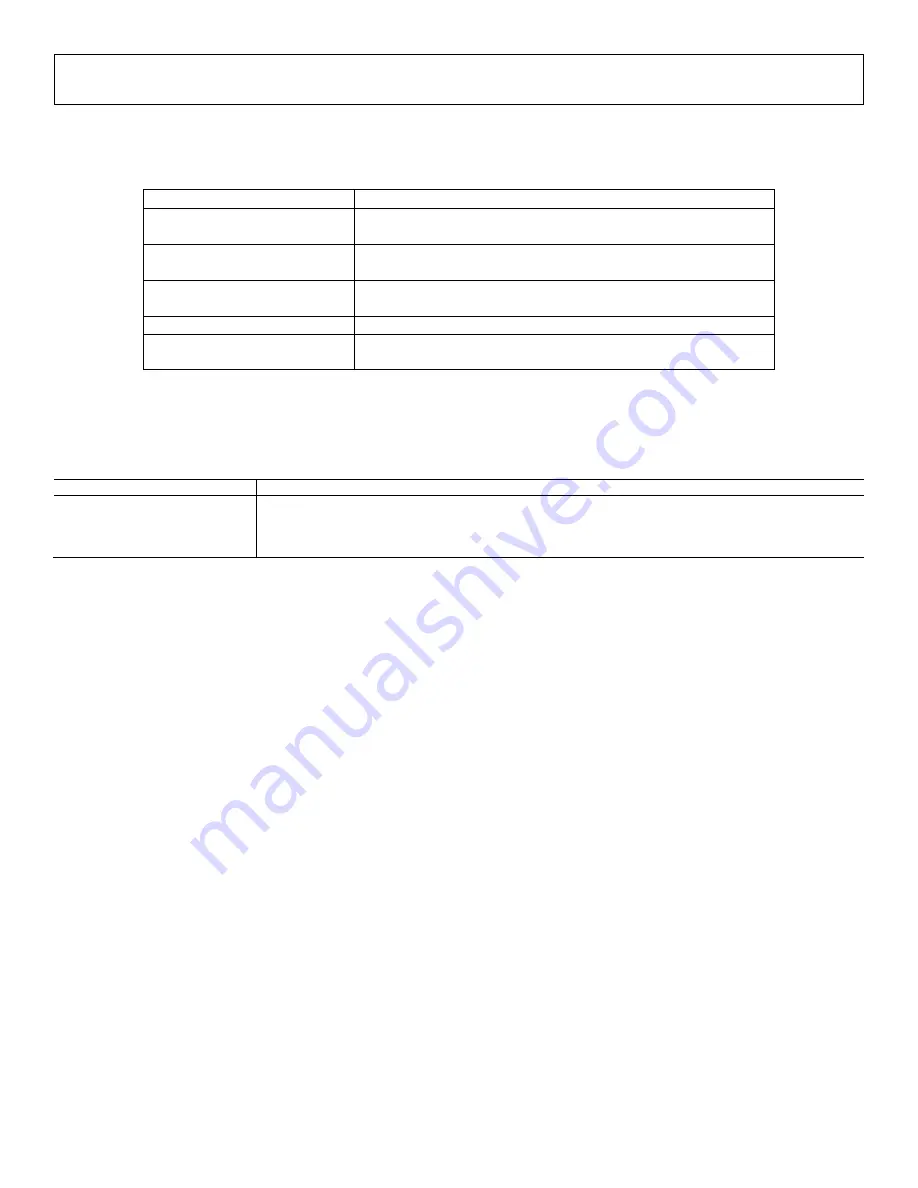

Table 86: VSP and OSD Interrupts

Interrupt

Description

OSD_CFG_DONE

Used to indicate to the system controller that the configuration within

the

RAM memories has completed

DMA_IRQ

Used to indicate to the system controller that the current DMA

operation has taken place

DMA_RAM_IRQ

Used to indicate to the system controller that the DMA hardware block

can be read from/written to by SPI

TIMER_IRQ

Used to indicate to the system controller that a timer has expired

ANIM_DONE_IRQ

Used to indicate to the system controller that an animation has

completed

The following controls are available to the user for indicating interrupts on the VSP and OSD interrupts.

vsp_int_pol[1:0]

, IO Map,

Address 0x1A76[3:2]

This signal is used to control the VSP interrupt polarity.

Function

vsp_int_pol[1:0]

Description

00 (default)

VSP interrupt is logical AND of VSP/OSD interrupts

01

VSP interrupt is inverted logical AND of VSP/OSD interrupts

10

VSP interrupt is logical OR of VSP/OSD interrupts

11

VSP interrupt is inverted logical OR of VSP/OSD interrupts

8.4.

HDMI TX CORE

8.4.1.

Introduction

This section describes the interrupt support provided for the HDMI Tx cores of the

. The HDMI Tx interrupts are OR’d together and

INT1 pin.

The

HDMI Tx interrupt architecture provides the following types of bits:

•

Interrupt status/clear bits

•

Interrupt mask bits

The interrupt status/clear bits are dual purpose; when an interrupt event or condition occurs, if the interrupt mask bit is set, the status bit gets

latched to 1. The interrupt can only be cleared by writing a value of 1 to the status/clear bit.

The interrupts mask bits are used to selectively activate an interrupt bit on the interrupt out pin INT1. The interrupt output pin is active when

one or more interrupts bits are set and their corresponding interrupt mask bit is also set. Note that any given mask bit does not affect its

corresponding interrupt bit but only affects the level on the interrupt output pin INT1. The enables for all the HDMI transmitter interrupts are

described below.

Rev. A | Page 286 of 317