System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-185

ID021414

Non-Confidential

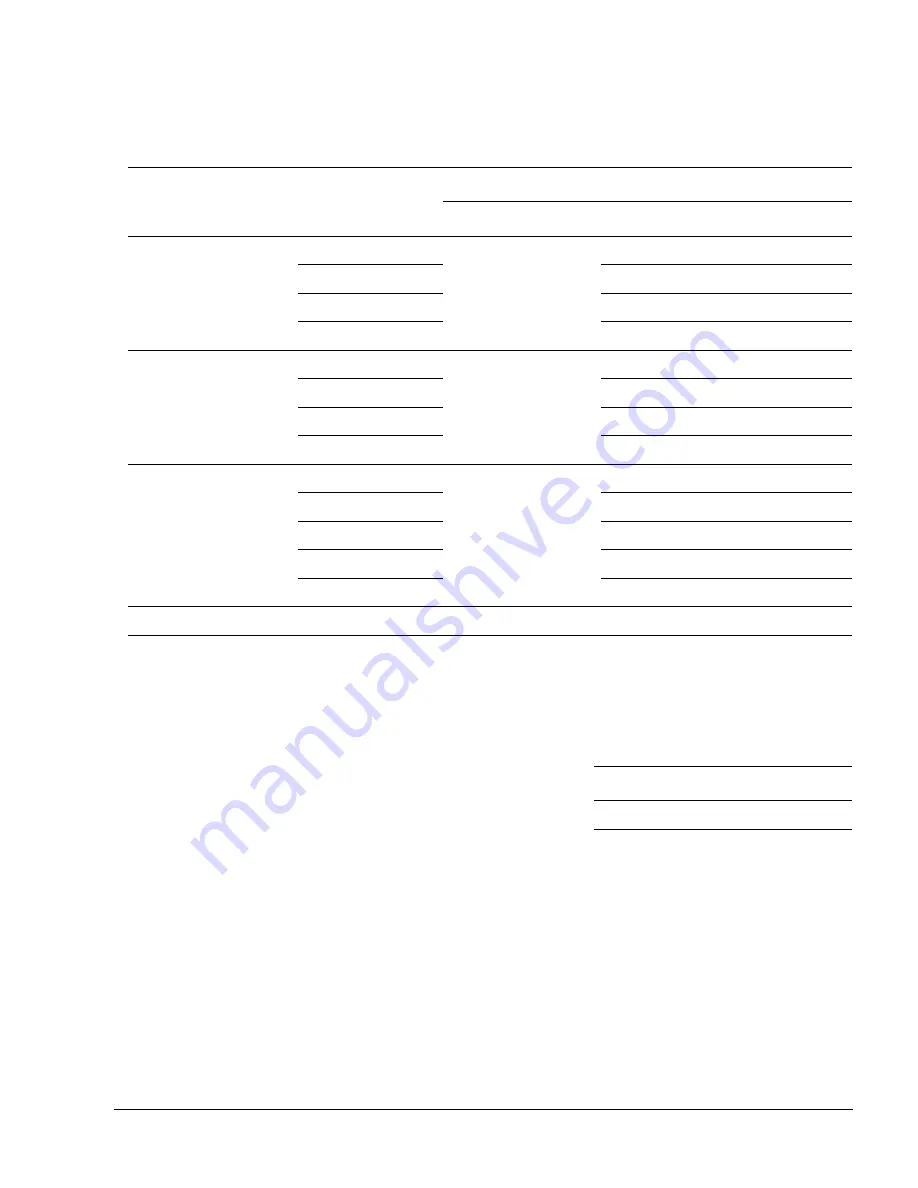

Table 4-181

shows the individual bit field and complete register encodings for the CCSIDR.

The CSSELR determines which CCSIDR to select.

To access the CCSIDR:

MRC p15, 1, <Rt>, c0, c0, 0 ; Read CCSIDR into Rt

Register access is encoded as follows:

4.5.21

Cache Level ID Register

The CLIDR characteristics are:

Purpose

Identifies:

•

The type of cache, or caches, implemented at each level.

•

The Level of Coherency and Level of Unification for the cache

hierarchy.

Table 4-181 CCSIDR encodings

CSSELR

Cache Size

Complete

register

encoding

Register bit field encoding

WT

WB

RA

WA

NumSets

Associativity

LineSize

0x0

L1 Data cache

8KB

0x7003E01A

0

1

1

1

0x001F

0x003

0x2

16KB

0x7007E01A

0x003F

0x003

0x2

32KB

0x700FE01A

0x007F

0x003

0x2

64KB

0x701FE01A

0x00FF

0x003

0x2

0x1

L1 Instruction

cache

8KB

0x2007E00A

0

0

1

0

0x003F

0x001

0x2

16KB

0x200FE00A

0x007F

0x001

0x2

32KB

0x201FE00A

0x00FF

0x001

0x2

64KB

0x203FE00A

0x001F

0x001

0x2

0x2

L2 cache

128KB

0x700FE07A

0

1

1

1

0x007F

0x00F

0x2

256KB

0x701FE07A

0x00FF

0x00F

0x2

512KB

0x703FE07A

0x01FF

0x00F

0x2

1024KB

0x707FE07A

0x03FF

0x00F

0x2

2048KB

0x70FFE07A

0x07FF

0x00F

0x2

0x3-0xF

Reserved

-

-

-

-

-

-

-

-

-

Table 4-182 CCSIDR access encoding

coproc

opc1

CRn

CRm

opc2

1111

001

0000

0000

000