Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-40

ID021414

Non-Confidential

The TRCIDR0 can be accessed through the internal memory-mapped interface and the external

debug interface, offset

0x1E0

.

13.8.32 ID Register 1

The TRCIDR1 characteristics are:

Purpose

Returns the base architecture of the trace unit.

Usage constraints

There are no usage constraints.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

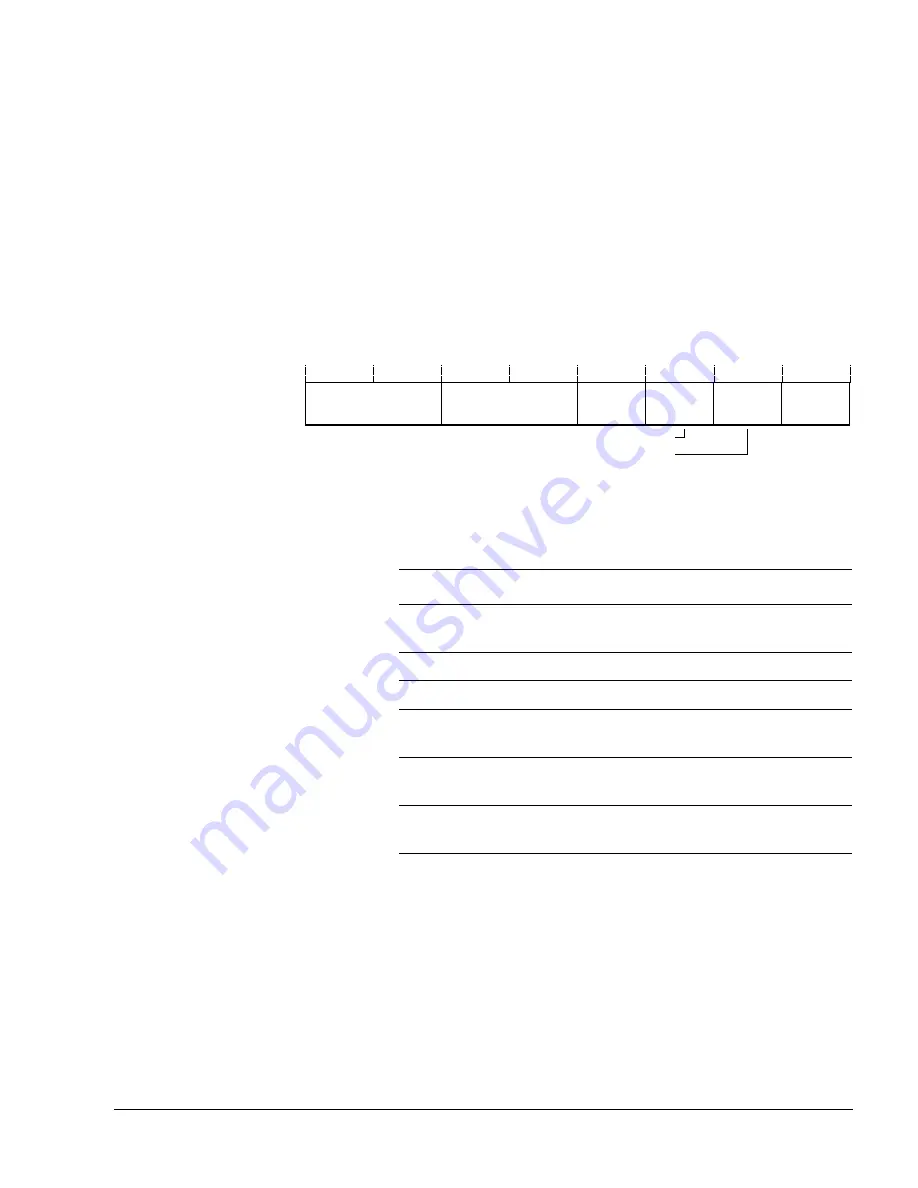

Figure 13-34

shows the TRCIDR1 bit assignments.

Figure 13-34 TRCIDR1 bit assignments

Table 13-35

shows the TRCIDR1 bit assignments.

The TRCIDR1 can be accessed through the internal memory-mapped interface and the external

debug interface, offset

0x1E4

.

13.8.33 ID Register 2

The TRCIDR2 characteristics are:

Purpose

Returns the maximum size of the following parameters in the trace unit:

•

Cycle counter.

•

Data value.

•

Data address.

•

VMID.

31

0

RES

0

TRCARCHMAJ

24 23

16 15

12 11

8 7

4 3

RES

1

DESIGNER

REVISION

TRCARCHMIN

Table 13-35 TRCIDR1 bit assignments

Bits

Name

Function

[31:24]

DESIGNER

Indicates which company designed the trace unit:

0x41

ARM.

[23:16]

-

Reserved,

RES

0.

[15:12]

-

Reserved,

RES

1.

[11:8]

TRCARCHMAJ

Major trace unit architecture version number:

0b0100

ETMv4.

[7:4]

TRCARCHMIN

Minor trace unit architecture version number:

0b0000

Minor revision 0.

[3:0]

REVISION

Implementation revision number:

0b0010

r0p2.