Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-56

ID021414

Non-Confidential

13.8.49 Integration ATB Identification Register

The TRCITATBIDR characteristics are:

Purpose

Sets the state of output pins shown in

Table 13-52

.

Usage constraints

•

Available when bit[0] of TRCITCTRL is set to 1.

•

The value of the register sets the signals on the output pins when the

register is written.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

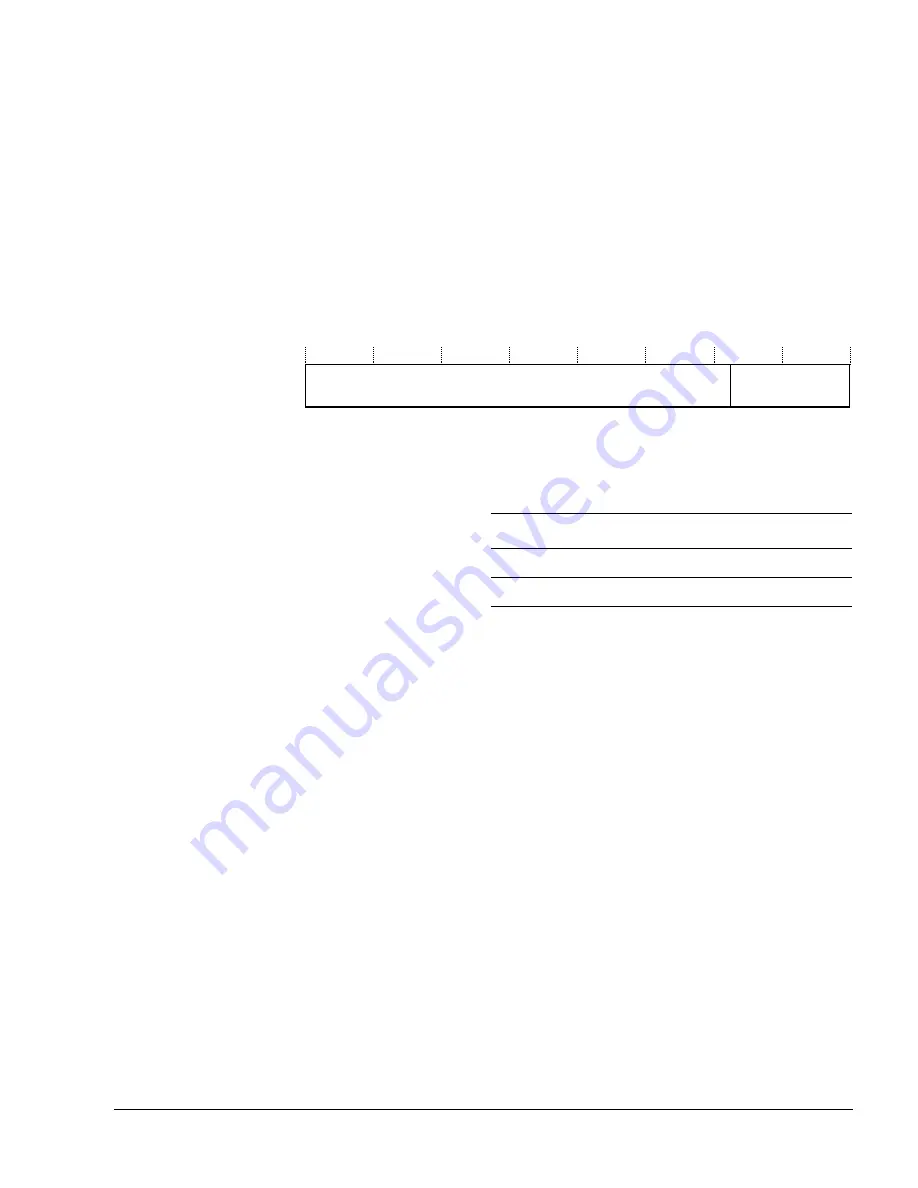

Figure 13-51

shows the TRCITATBIDR bit assignments.

Figure 13-51 TRCITATBIDR bit assignments

Table 13-52

shows the TRCITATBIDR bit assignments.

The TRCITATBIDR can be accessed through the internal memory-mapped interface and the

external debug interface, offset

0xEE4

.

13.8.50 Integration Instruction ATB Data Register

The TRCITIDATAR characteristics are:

Purpose

Sets the state of the

ATDATAMn

output pins shown in

Table 13-53 on

page 13-57

.

Usage constraints

•

Available when bit[0] of TRCITCTRL is set to 1.

•

The value of the register sets the signals on the output pins when the

register is written.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

Figure 13-52 on page 13-57

shows the TRCITIDATAR bit assignments.

ID

Reserved

31

0

7 6

Table 13-52 TRCITATBIDR bit assignments

Bits

Name

Function

[31:7]

-

Reserved. Read undefined.

[6:0]

ID

Drives the

ATIDMn[6:0]

output pins

a

.

a. When a bit is set to 0, the corresponding output pin is LOW.

When a bit is set to 1, the corresponding output pin is HIGH.

The TRCITATBIDR bit values correspond to the physical

state of the output pins.