Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-18

ID021414

Non-Confidential

The TRCAUXCTLR can be accessed through the internal memory-mapped interface and the

external debug interface, offset

0x018

.

13.8.6

Event Control 0 Register

The TRCEVENTCTL0R characteristics are:

Purpose

Controls the tracing of events in the trace stream. The events also drive the

external outputs from the ETM trace unit. The events are selected from the

Resource Selectors.

Usage constraints

•

You must always program this register as part of trace unit

initialization.

•

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

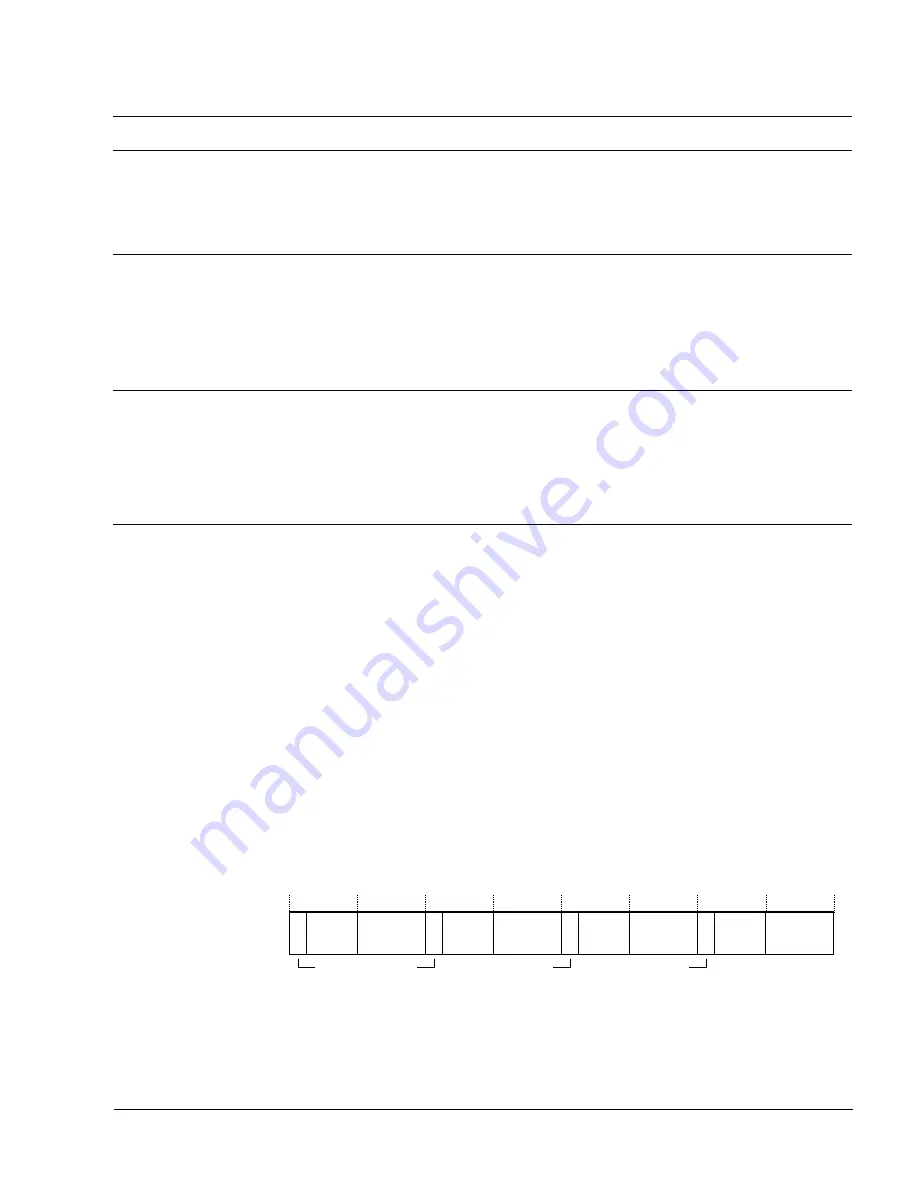

Figure 13-8

shows the TRCEVENTCTL0R bit assignments.

Figure 13-8 TRCEVENTCL0R bit assignments

[2]

OVFLW

Force an overflow if synchronization is not completed when second synchronization becomes

due. The possible values are:

0

No FIFO overflow when SYNC packets are delayed.

1

Forces FIFO overflow when SYNC packets are delayed.

When this bit is set to 1, the trace unit behavior deviates from architecturally-specified behavior.

[1]

IDLEACK

Force idle-drain acknowledge high, CPU does not wait for trace to drain before entering WFX

state. The possible values are:

0

ETM trace unit idle acknowledge is asserted only when the ETM trace unit is

in idle state.

1

ETM trace unit idle acknowledge is asserted irrespective of the ETM trace unit

idle state.

When this bit is set to 1, trace unit behavior deviates from architecturally-specified behavior.

[0]

AFREADY

Always respond to AFREADY immediately. Does not have any interaction with FIFO draining,

even in WFI state. The possible values are:

0

ETM trace unit

AFREADYM

output is asserted only when the ETM trace unit

is in idle state or when all the trace bytes in FIFO before a flush request are

output.

1

ETM trace unit

AFREADYM

output is always asserted HIGH. When this bit

is set to 1, trace unit behavior deviates from architecturally-specified behavior.

Table 13-8 TRCAUXCTLR bit assignments (continued)

Bits

Name

Function

RES

0

RES

0

RES

0

31

16 15 14

12 11

8 7

4 3

0

RES

0

TYPE3

SEL1

30

28 27

24 23 22

20 19

SEL3

SEL2

TYPE2

TYPE0

TYPE1

SEL0

6