System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-124

ID021414

Non-Confidential

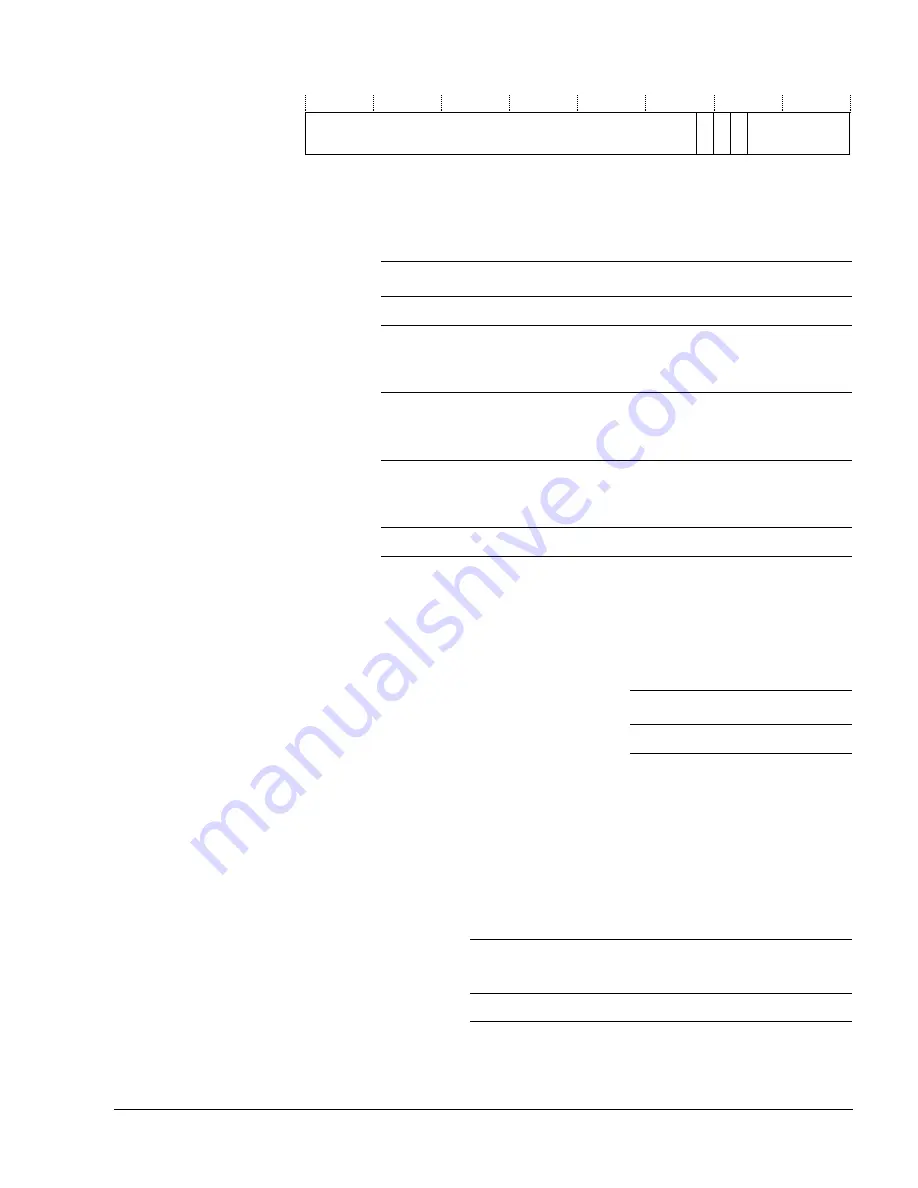

Figure 4-70 ISR_EL1 bit assignments

Table 4-114

shows the ISR_EL1 bit assignments.

To access the ISR_EL1:

MRS <Xt>, ISR_EL1 ; Read ISR_EL1 into Xt

Register access is encoded as follows:

4.3.78

CPU Auxiliary Control Register, EL1

The CPUACTLR_EL1 characteristics are:

Purpose

Provides

IMPLEMENTATION

DEFINED

configuration and control options for

the processor. There is one 64-bit CPU Auxiliary Control Register for each

core in the cluster.

Usage constraints

This register is accessible as follows:

31

9 8 7 6 5

0

Reserved

F

I

A

Reserved

Table 4-114 ISR_EL1 bit assignments

Bits

Name

Function

[31:9]

-

Reserved,

RES

0.

[8]

A

External abort pending bit:

0

No pending external abort.

1

An external abort is pending.

[7]

I

IRQ pending bit. Indicates whether an IRQ interrupt is pending:

0

No pending IRQ.

1

An IRQ interrupt is pending.

[6]

F

FIQ pending bit. Indicates whether an FIQ interrupt is pending:

0

No pending FIQ.

1

An FIQ interrupt is pending.

[5:0]

-

Reserved,

RES

0.

Table 4-115 ISR_EL1 access encoding

op0

op1

CRn

CRm

op2

11

000

1100

0001

000

EL0

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

RW

RW

RW

RW

RW