Generic Interrupt Controller CPU Interface

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

9-6

ID021414

Non-Confidential

Table 9-5

describes the registers for the virtual interface control registers.

All the registers in

Table 9-5

are word-accessible. Registers not described in this table are

RES

0.

See the

ARM

®

Generic Interrupt Controller Architecture Specification

for more information.

9.2.5

Virtual interface control register descriptions

This section describes only registers whose implementation is specific to the Cortex-A53

processor. All other registers are described in the

ARM

®

Generic Interrupt Controller

Architecture Specification

.

Table 9-5

provides cross-references to individual registers.

VGIC Type Register

The GICH_VTR characteristics are:

Purpose

Holds information on number of priority bits, number of preemption bits,

and number of List Registers implemented.

Usage constraints

There are no usage constraints.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 9-5

.

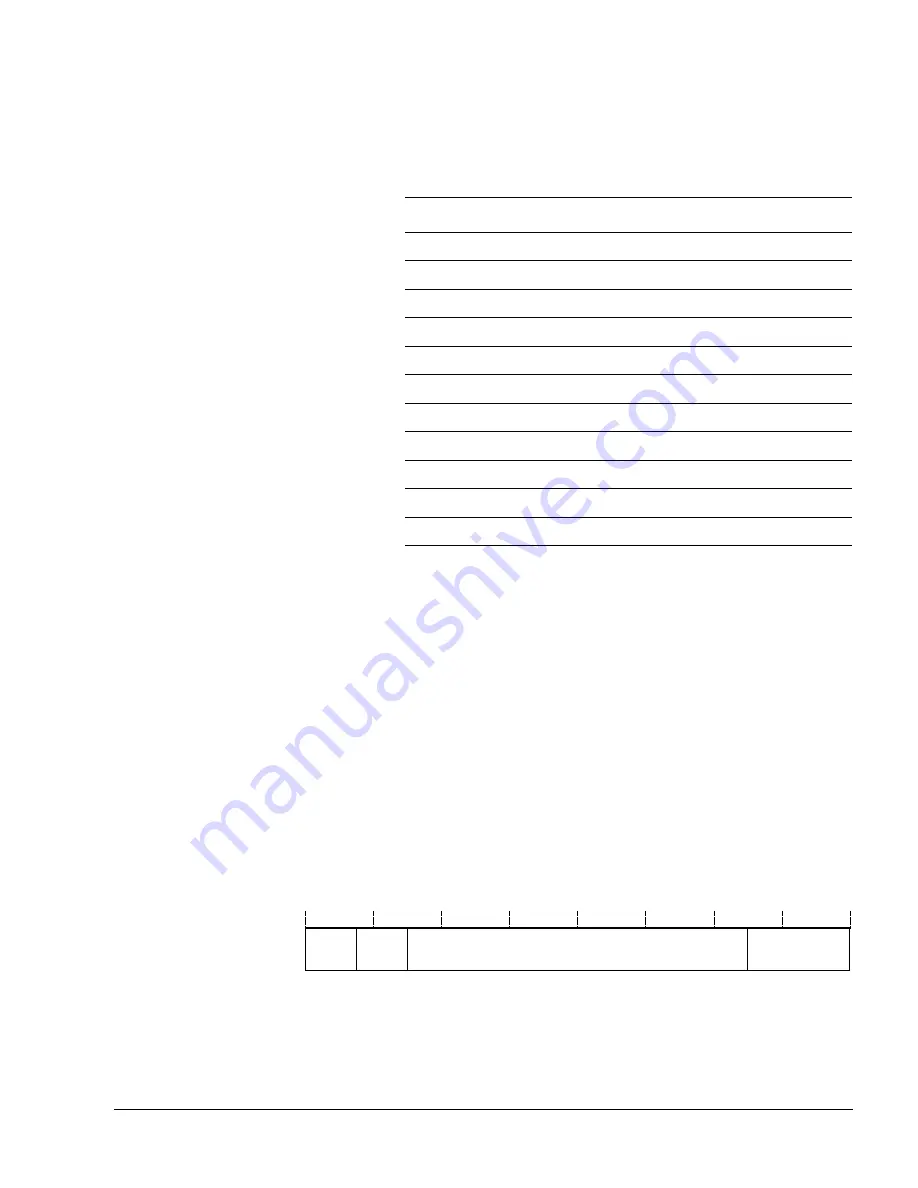

Figure 9-2

shows the GICH_VTR bit assignments.

Figure 9-2 GICH_VTR bit assignments

Table 9-5 Virtual interface control register summary

Name

Type

Reset

Description

GICH_HCR

RW

0x00000000

Hypervisor Control Register

GICH_VTR

RO

0x90000003

VGIC Type Register

GICH_VMCR

RW

0x004C0000

Virtual Machine Control Register

GICH_MISR

RO

0x00000000

Maintenance Interrupt Status Register

GICH_EISR0

RO

0x00000000

End of Interrupt Status Registers

GICH_ELSR0

RO

0x0000000F

Empty List Register Status Registers

GICH_APR0

RW

0x00000000

Active Priorities Register

GICH_LR0

RW

0x00000000

List Register 0

GICH_LR1

RW

0x00000000

List Register 1

GICH_LR2

RW

0x00000000

List Register 2

GICH_LR3

RW

0x00000000

List Register 3

PRIbits

31

29 28

26 25

6 5

0

PREbits

RES

0

ListRegs