Level 2 Memory System

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

7-14

ID021414

Non-Confidential

In a CHI configured Cortex-A53 processor, there is no fixed mapping between CHI transaction

IDs and cores. Some transaction IDs can be used for either reads or writes.

See the

ARM

®

AMBA

®

5 CHI Protocol Specification

for more information about the CHI signals

described in this manual.

7.4.2

CHI transfers

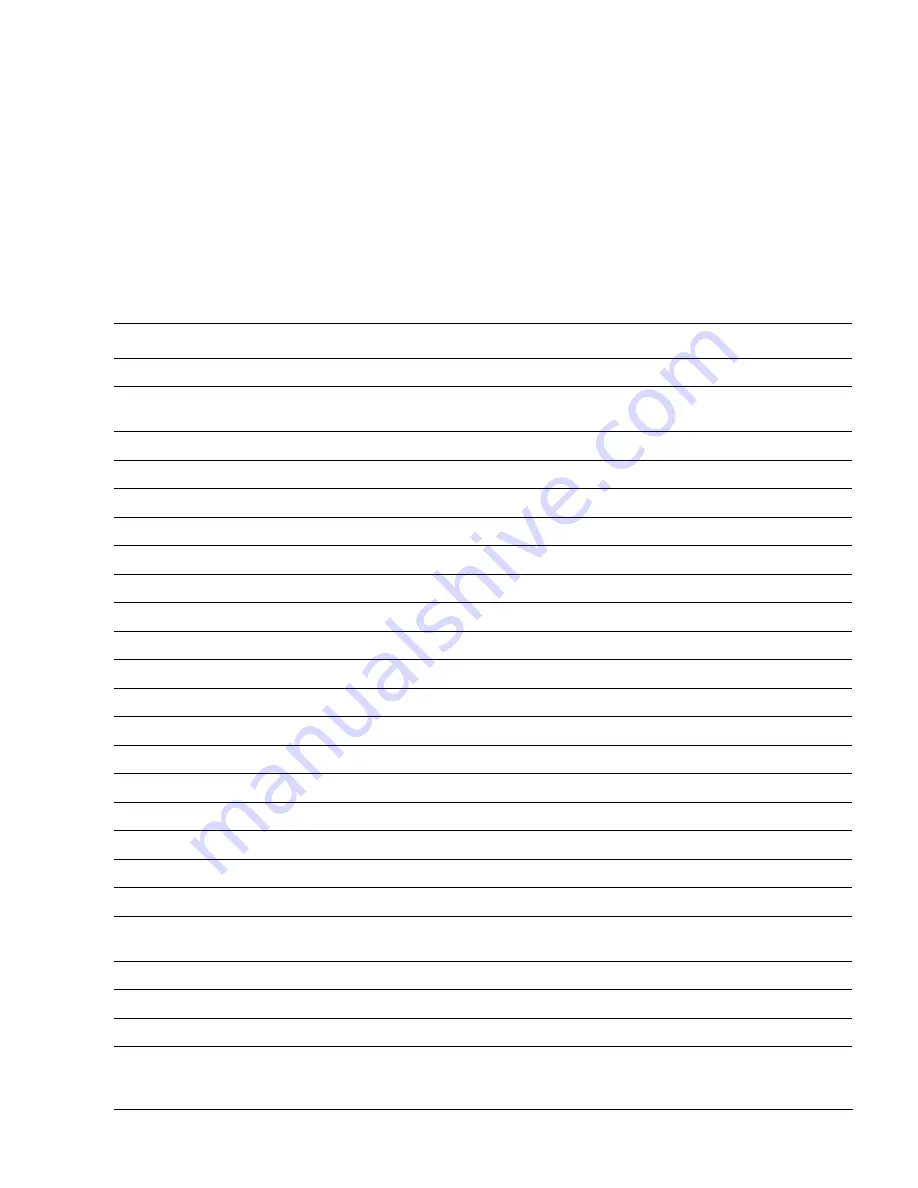

Table 7-12

shows the CHI transactions that can be generated, and some typical operations that

might cause the transactions to be generated. This is not an exhaustive list of ways to generate

each type of transaction, because there are many possibilities.

Table 7-12 CHI transactions

Transaction

Operation

ReadNoSnp

Non-cacheable loads or instruction fetches. Linefills of non-shareable cache lines into L1 or L2.

ReadOnce

Cacheable loads that are not allocating into the cache, or cacheable instruction fetches when there is no L2

cache.

ReadClean

Not used.

ReadShared

L1 Data linefills started by a load instruction, or L2 linefills started by an instruction fetch.

ReadUnique

L1 Data linefills started by a store instruction.

CleanUnique

Store instructions that hit in the cache but the line is not in a unique coherence state.

MakeUnique

Store instructions of a full cache line of data, that miss in the caches, and are allocating into the L2 cache.

CleanShared

Cache maintenance instructions.

CleanInvalid

Cache maintenance instructions.

MakeInvalid

Cache maintenance instructions.

DVMOp

TLB and instruction cache maintenance instructions.

EOBarrier

DMB instructions.

ECBarrier

DSB instructions. DVM sync snoops received from the interconnect.

WriteNoSnpPtl

Non-cacheable store instructions.

WriteNoSnpFull

Non-cacheable store instructions, or evictions of non-shareable cache lines from the L1 and L2 cache.

WriteUniqueFull

Cacheable writes of a full cache line, that are not allocating into L1 or L2 caches, for example streaming writes.

WriteLineUniquePtl

Cacheable writes of less than a full cache line that are not allocating into L1 or L2.

WriteBackFull

Evictions of dirty lines from the L1 or L2 cache.

WriteBackPtl

Not used.

WriteCleanFull

Evictions of dirty lines from the L2 cache, when the line is still present in an L1 cache. Some cache

maintenance instructions.

WriteCleanPtl

Not used.

WriteEvictFull

Evictions of unique clean lines, when configured in the L2ACTLR.

Evict

Evictions of clean lines, when configured in the L2ACTLR.