Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-43

ID021414

Non-Confidential

The TRCIDR3 can be accessed through the internal memory-mapped interface and the external

debug interface, offset

0x1EC

.

13.8.35 ID Register 4

The TRCIDR4 characteristics are:

Purpose

Indicates the resources available in the ETM trace unit.

Usage constraints

There are no usage constraints.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

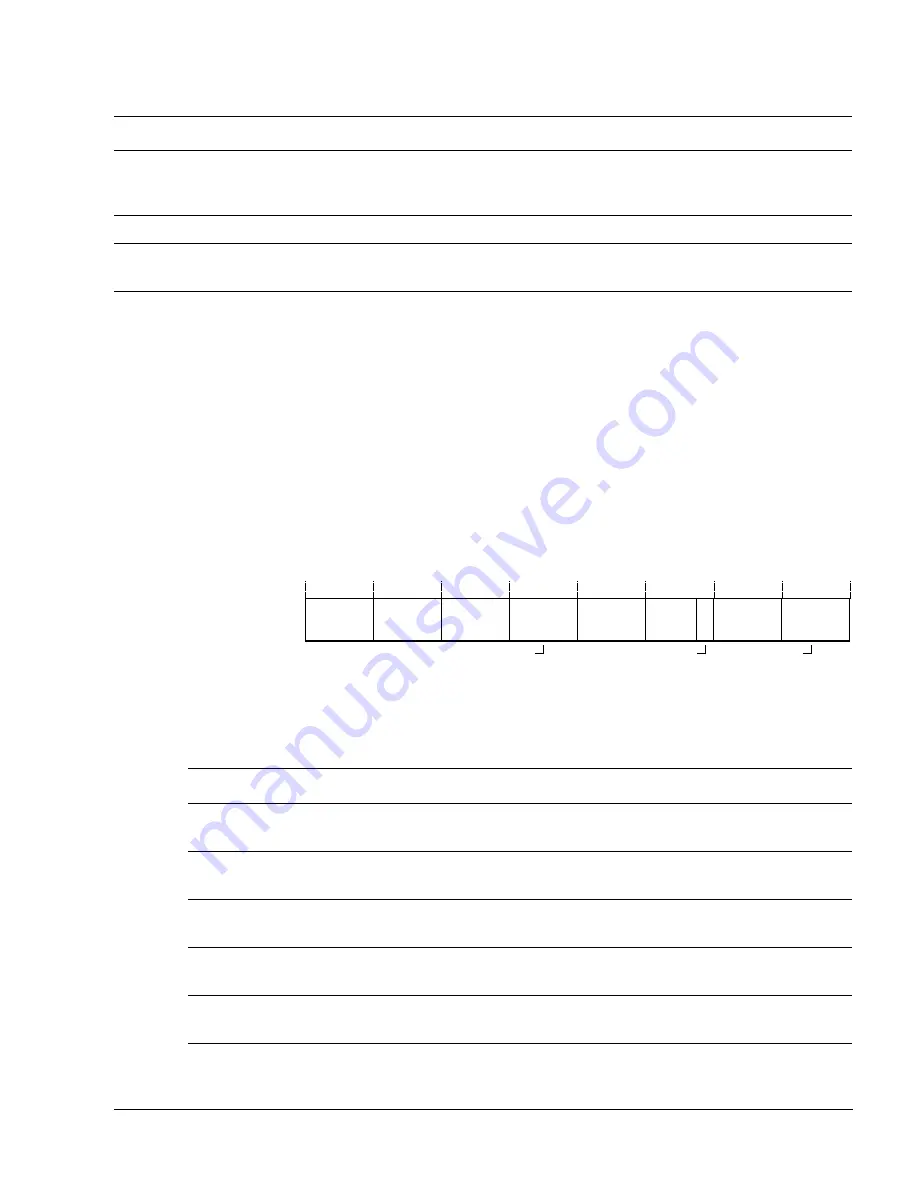

Figure 13-37

shows the TRCIDR4 bit assignments.

Figure 13-37 TRCIDR4 bit assignments

Table 13-38

shows the TRCIDR4 bit assignments.

[19:16]

EXLEVEL_S

Each bit controls whether instruction tracing in Secure state is implemented for the corresponding

exception level:

0b1011

Instruction tracing is implemented for Secure EL0, EL1 and EL3 exception levels.

[15:12]

-

Reserved,

RES

0.

[11:0]

CCITMIN

The minimum value that can be programmed in TRCCCCTLR.THRESHOLD:

0x004

Instruction trace cycle counting minimum threshold is 4.

Table 13-37 TRCIDR3 bit assignments (continued)

Bits

Name

Function

31

0

23

24

16 15

8 7

3

4

27

28

20 19

NUMDVC

NUMPC

NUMSSCC

NUMCIDC

NUMACPAIRS

9

11

12

NUMRCPAIRS

NUMVMIDC

SUPPDAC

RES

0

Table 13-38 TRCIDR4 bit assignments

Bits

Name

Function

[31:28]

NUMVMIDC

Indicates the number of VMID comparators available for tracing:

0x1

One VMID comparator is available.

[27:24]

NUMCIDC

Indicates the number of CID comparators available for tracing:

0x1

One Context ID comparator is available.

[23:20]

NUMSSCC

Indicates the number of single-shot comparator controls available for tracing:

0x1

One single-shot comparator control is available.

[19:16]

NUMRSPAIR

Indicates the number of resource selection pairs available for tracing:

0x7

Eight resource selection pairs are available.

[15:12]

NUMPC

Indicates the number of processor comparator inputs available for tracing:

0x0

Processor comparator inputs are not implemented.

[11:9]

-

Reserved,

RES

0.