Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-46

ID021414

Non-Confidential

Table 13-40

shows the TRCRSCTLRn bit assignments.

The TRCRSCTLRn can be accessed through the internal memory-mapped interface and the

external debug interface, offset

0x208-023C

.

13.8.38 Single-Shot Comparator Control Register 0

The TRCSSCCR0 characteristics are:

Purpose

Controls the single-shot comparator.

Usage constraints

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

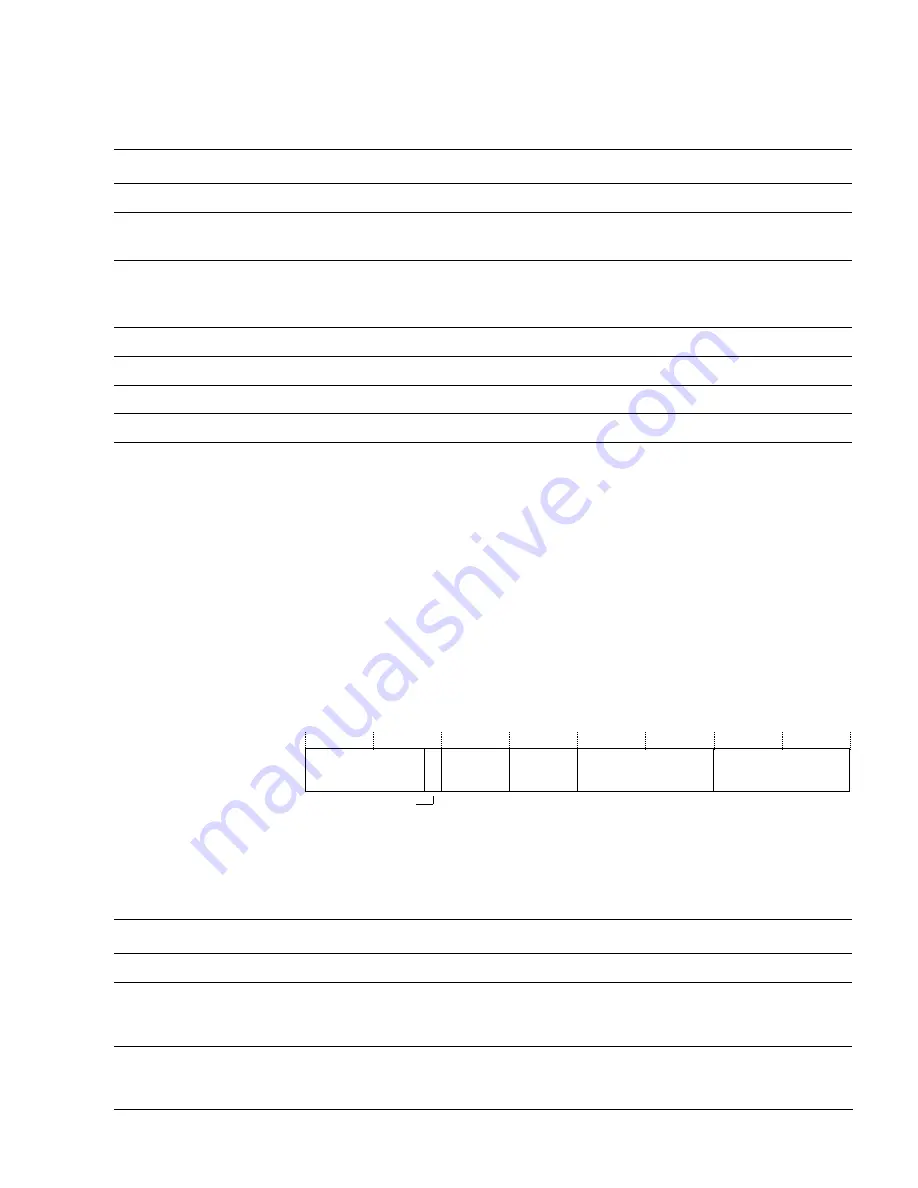

Figure 13-40

shows the TRCSSCCR0 bit assignments.

Figure 13-40 TRCSSCCR0 bit assignments

Table 13-41

shows the TRCSSCCR0 bit assignments.

Table 13-40 TRCSCTLR

n

bit assignments

Bits

Name

Function

[31:22]

-

Reserved,

RES

0.

[21]

PAIRINV

Inverts the result of a combined pair of resources.

This bit is implemented only on the lower register for a pair of resource selectors.

[20]

INV

Inverts the selected resources:

0

Resource is not inverted.

1

Resource is inverted.

[19]

-

Reserved,

RES

0.

[18:16]

GROUP

Selects a group of resources. See the

ARM

®

ETM

™

Architecture Specification, ETMv4

for more information.

[15:8]

-

Reserved,

RES

0.

[7:0]

SELECT

Selects one or more resources from the required group. One bit is provided for each resource from the group.

RES

0

RES

0

31

20 19

16 15

8 7

0

ARC

RES

0

SAC

24 23

25

RST

Table 13-41 TRCSSCCR0 bit assignments

Bits

Name

Function

[31:25]

-

Reserved,

RES

0.

[24]

RST

Enables the single-shot comparator resource to be reset when it occurs, to enable another comparator match to be

detected:

1

Reset enabled. Multiple matches can occur.

[23:20]

-

Reserved,

RES

0.