Developer’s Manual

January, 2004

129

Intel XScale® Core

Developer’s Manual

Software Debug

9.5.2

Monitor Mode

In Monitor Mode, the processor handles debug exceptions like normal ARM exceptions, except for

SOC debug breaks, which are handled like Halt Mode exceptions. If debug functionality is enabled

and the processor is in Monitor Mode, debug exceptions cause either a data abort or a pre-fetch abort.

The following debug exceptions cause data aborts:

•

data breakpoint

•

external debug break

•

trace-buffer full break

The following debug exceptions cause pre-fetch aborts:

•

instruction breakpoint

•

BKPT instruction

The processor ignores vector traps during Monitor Mode.

When an exception occurs in Monitor Mode, the processor takes the following actions:

•

disables the trace buffer

•

sets DCSR.moe encoding

•

sets FSR[9]

•

R14_DBG is updated as follows:

•

SPSR_abt = CPSR

•

CPSR[4:0] = 0b10111 (ABORT mode)

•

CPSR[5] = 0

•

CPSR[6] = unchanged

•

CPSR[7] = 1

•

PC = 0xC or 0xFFFF000C (for Prefetch Aborts),

PC = 0x10 or 0xFFFF0010 (for Data Aborts)

During abort mode, external debug breaks and trace buffer full breaks are internally pended. When

the processor exits abort mode, either through a CPSR restore or a write directly to the CPSR, the

pended debug breaks will immediately generate a debug exception. Any pending debug breaks are

cleared out when any type of debug exception occurs. Note that SOC debug breaks are not pended

during abort mode; they are handled immediately when detected.

When exiting, the debug handler should do a CPSR restore operation that branches to the next

instruction to be executed in the program under debug.

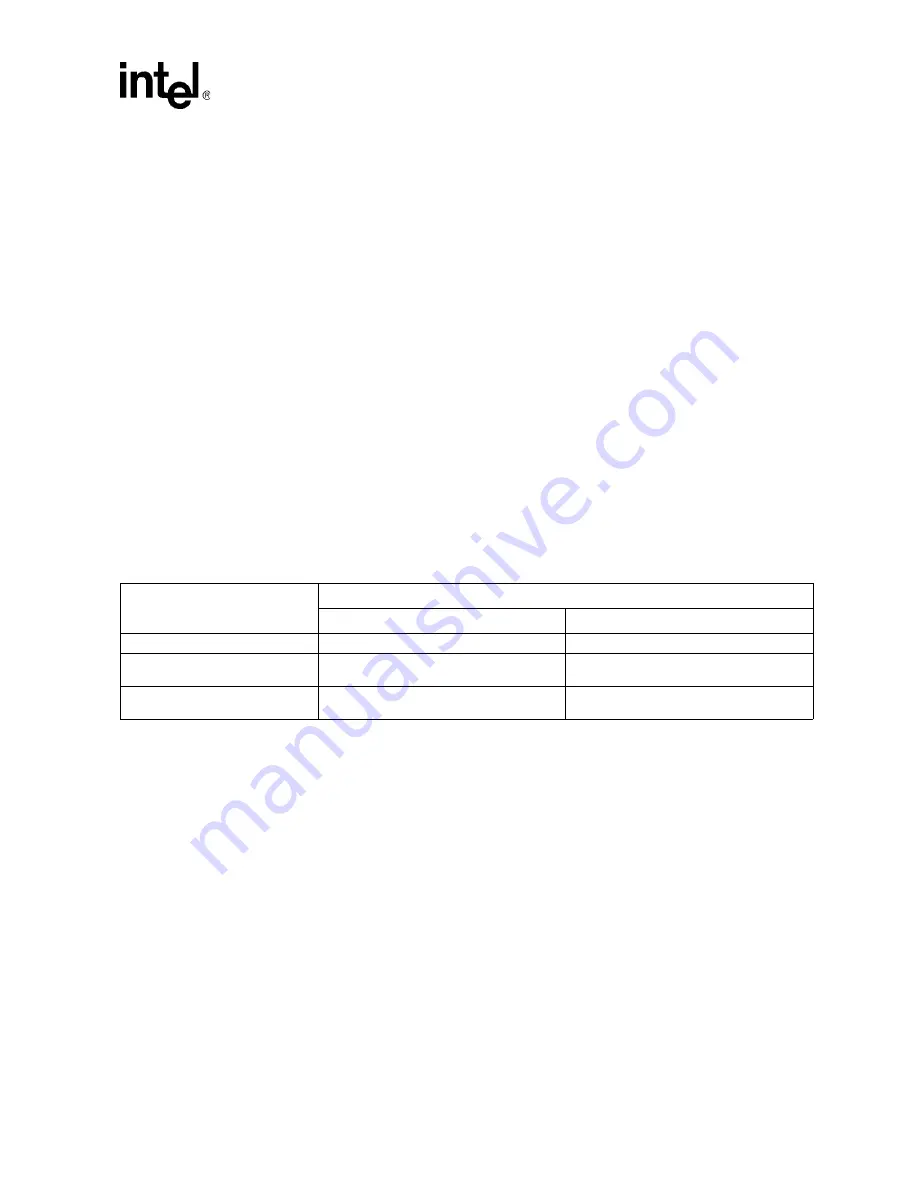

Table 9-4.

Monitor Mode R14_DBG Updating

Debug Exception Type

DBG_r14 Value

ARM mode

Thumb mode

Data Breakpoint

PC of breakpointed memory instr 8

PC of breakpointed memory instr 6

Instruction Breakpoint,

SW Breakpoint

PC of breakpointed instr 4

PC of breakpointed instr 4

Trace Buffer Full Break,

External Debug Break

PC of next instruction to e 4

PC of next instruction to e 4