Developer’s Manual

January, 2004

91

Intel XScale® Core

Developer’s Manual

Configuration

7.2.11

Register 10: TLB Lock Down

Register 10 is used for locking down entries into the instruction TLB, and data TLB. (The protocol

for locking down entries can be found in

Chapter 3, “Memory Management”

.) Lock/unlock

operations on a TLB when the MMU is disabled have an undefined effect.

This register should be accessed as write-only. Reads from this register, as with an MRC, have an

undefined effect.

Table 7-16

shows the command for locking down entries in the instruction TLB, and data TLB.

The entry to lock is specified by the virtual address in Rd.

7.2.12

Register 11-12: Reserved

These registers are reserved. Reading and writing them yields unpredictable results.

7.2.13

Register 13: Process ID

The Intel XScale

®

core supports remapping of virtual addresses through a Process ID (PID) register.

This remapping occurs before the instruction cache, instruction TLB, data cache and data TLB are

accessed. The PID register controls when virtual addresses are remapped and to what value.

The PID register is a 7-bit value that replaces bits 31:25 of the virtual address when they are zero.

This effectively remaps the address to one of 128 “slots” in the 4 Gbytes of address space. If

bits 31:25 are not zero, no remapping occurs. This feature is useful for operating system

management of processes that may map to the same virtual address space. In those cases, the

virtually mapped caches on the core would not require invalidating on a process switch.

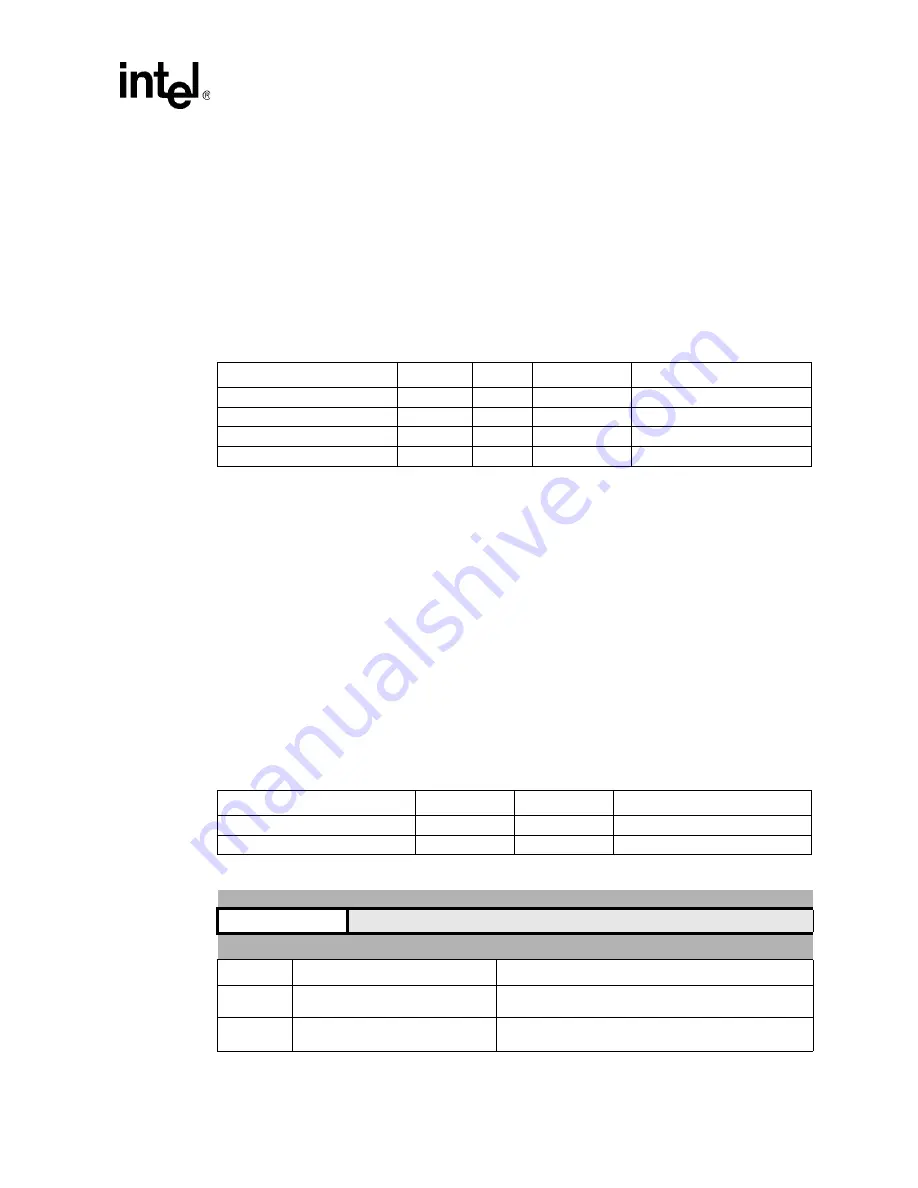

Table 7-16.

TLB Lockdown Functions

Function

opcode_2

CRm

Data

Instruction

Translate and Lock I TLB entry

0b000

0b0100

MVA

MCR p15, 0, Rd, c10, c4, 0

Translate and Lock D TLB entry

0b000

0b1000

MVA

MCR p15, 0, Rd, c10, c8, 0

Unlock I TLB

0b001

0b0100

Ignored

MCR p15, 0, Rd, c10, c4, 1

Unlock D TLB

0b001

0b1000

Ignored

MCR p15, 0, Rd, c10, c8, 1

Table 7-17.

Accessing Process ID

Function

opcode_2

CRm

Instruction

Read Process ID Register

0b000

0b0000

MRC p15, 0, Rd, c13, c0, 0

Write Process ID Register

0b000

0b0000

MCR p15, 0, Rd, c13, c0, 0

Table 7-18.

Process ID Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Process ID

reset value: 0x0000,0000

Bits

Access

Description

31:25

Read / Write

Process ID

- This field is used for remapping the virtual

address when bits 31-25 of the virtual address are zero.

24:0

Read-as-Zero / Write-as-Zero

Reserved

- Should be programmed to zero for future

compatibility