Developer’s Manual

January, 2004

57

Intel XScale® Core

Developer’s Manual

Branch Target Buffer

Branch Target Buffer

5

The Intel XScale

®

core uses dynamic branch prediction to reduce the penalties associated with

changing the flow of program execution. The core features a branch target buffer that provides the

instruction cache with the target address of branch type instructions. The branch target buffer is

implemented as a 128-entry, direct mapped cache.

This chapter is primarily for those optimizing their code for performance. An understanding of the

branch target buffer is needed in this case so that code can be scheduled to best utilize the

performance benefits of the branch target buffer.

5.1

Branch Target Buffer (BTB) Operation

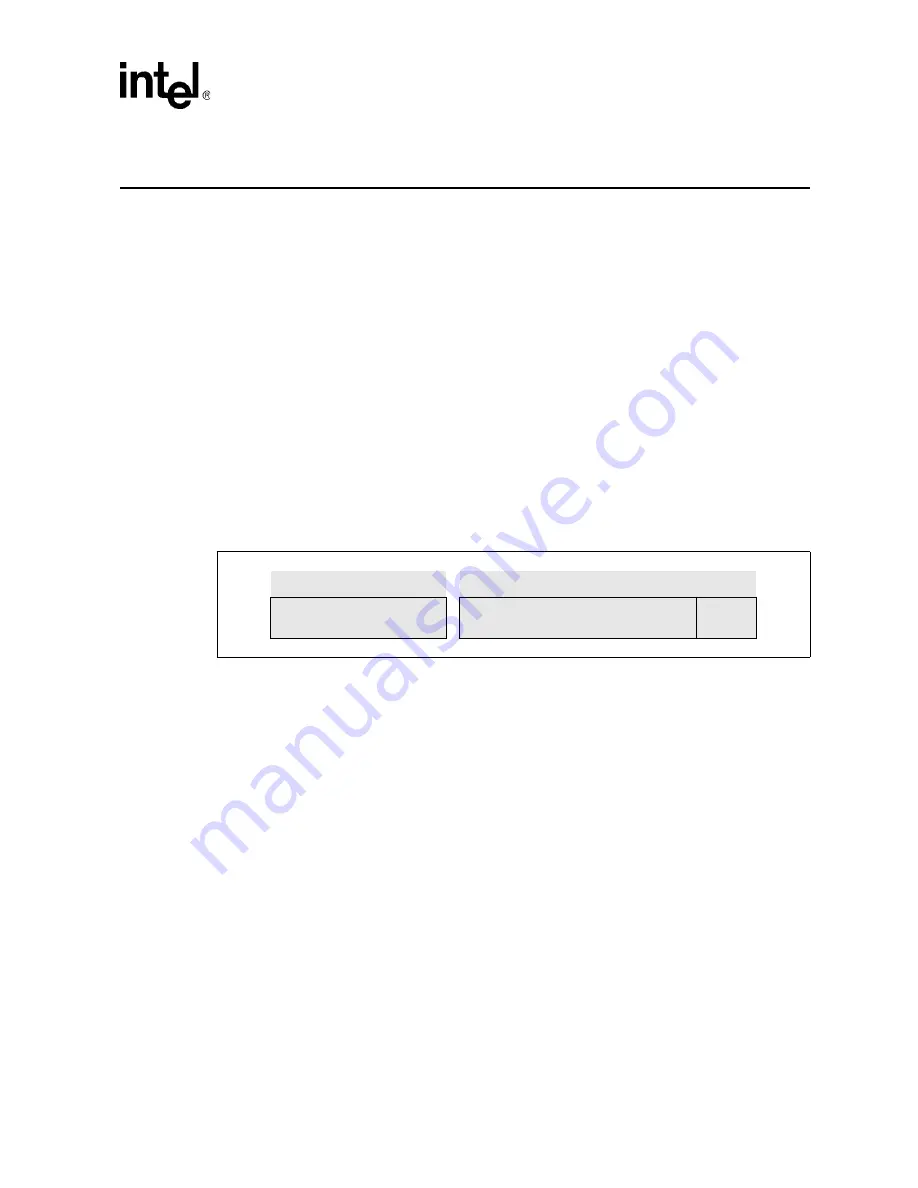

The BTB stores the history of branches that have executed along with their targets.

Figure 5-1

shows an entry in the BTB, where the tag is the instruction address of a previously executed branch

and the data contains the target address of the previously executed branch along with two bits of

history information.

The BTB takes the current instruction address and checks to see if this address is a branch that was

previously seen. It uses bits [8:2] of the current address to read out the tag and then compares this

tag to bits [31:9,1] of the current instruction address. If the current instruction address matches the

tag in the cache and the history bits indicate that this branch is usually taken in the past, the BTB

uses the data (target address) as the next instruction address to send to the instruction cache.

Bit[1] of the instruction address is included in the tag comparison in order to support Thumb

execution. This organization means that two consecutive Thumb branch (B) instructions, with

instruction address bits[8:2] the same, will contend for the same BTB entry. Thumb also requires

31 bits for the branch target address. In ARM mode, bit[1] is zero.

Figure 5-1.

BTB Entry

Branch Address[31:9,1]

Target Address[31:1]

History

DATA

TAG

Bits[1:0]