IP482 Industrial I/O Pack User’s Manual Counter Timer Module

___________________________________________________________________

________________________________________________________________________________________

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com http://www.acromag.com

39

1. Connect the inputs/output to the following pins (unpowered):

Pin # Connection

Description

5

In5_A(+)

Reload

15

In5_B(+)

Ext. Clock

25

In5_C(+)

Ext. Trigger

37

Out5(+)

Output

2. Write the following information, B56BH, to Counter 5 Control Register

located at base address plus an offset of 10H.

Bits

Logic

Operation

2,1,0

011

Sets the counter to Watchdog mode.

3

1

Sets the output to active high.

5,4

10

Enable the Counter Reload input (InA) to active high.

7,6

01

Enables the external clock input (InB).

9,8

01

Enables the external Trigger Input (InC) to active low.

12,11,10

101

Sets the clock to an external source.

13

1

Enables input debounce on InA and InC.

14

0

Not used.

15

1

Enables interrupts.

3. Write the 16-bit value 5H to Counter 5 Constant A Register located at the

base address plus an offset of 38H.

In order to determine the correct Constant A Register value, first

calculate the period of the selected clock. The period is calculated by taking

the inverse of the clock frequency. In this case, 1/500KHz is equal to 2

s.

Then take the total duration of the watchdog timer and divide it by the clock

period. For this example, 10

s/2

s is equal to five. Converted to Hex, this

is the number to write to the Counter 5 Constant A Register.

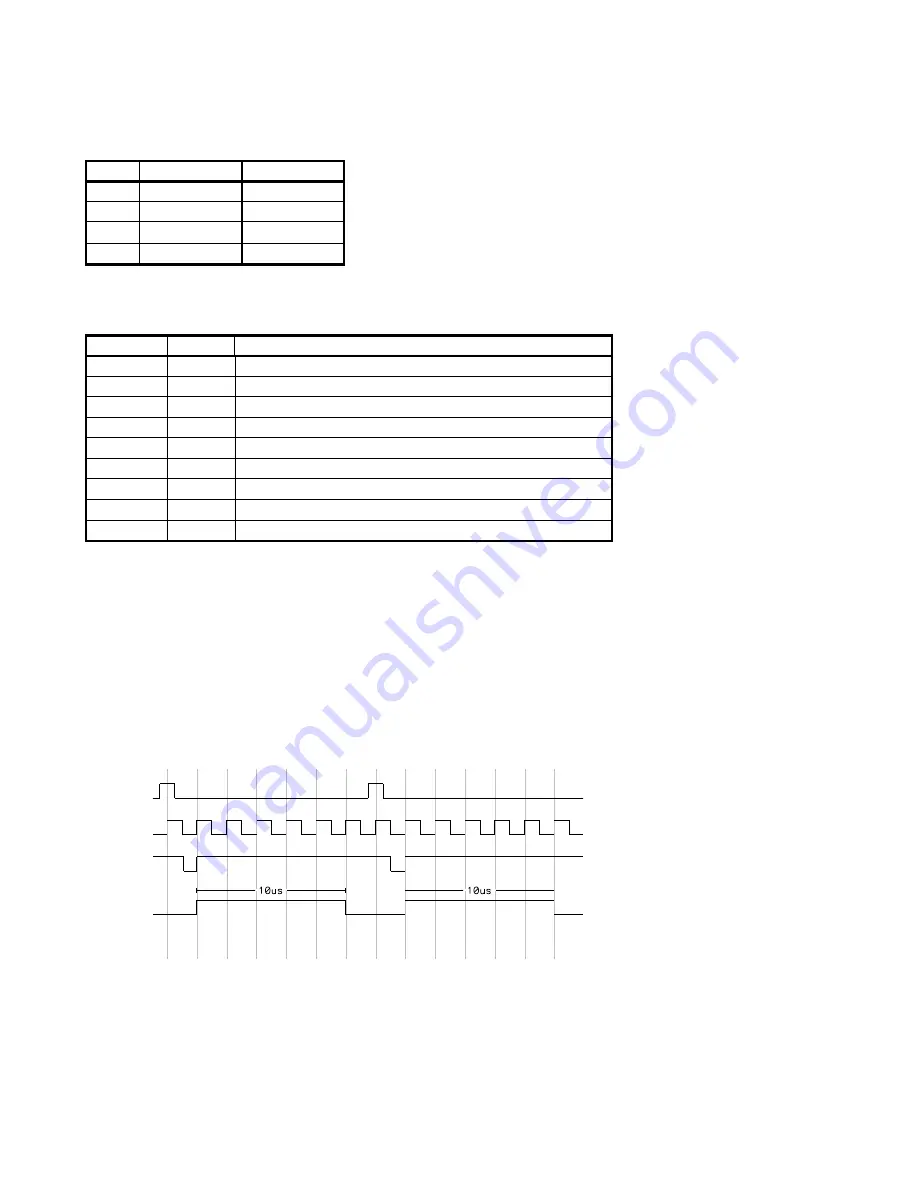

4. The following is a waveform diagram of this example.

i

i

Output

InB

InC

InA

Interrupts

In Watchdog mode, the counter must be loaded (InA) and then triggered

(InC) for each cycle. While this can be done internally or externally, failure to

follow this procedure will cause unpredictable results.

PROGRAMMING

EXAMPLES

Table 3.22:

Watchdog Pin

Assignments for Counter 5

Note: Make sure all inputs

and outputs are properly

grounded.

Table 3.23:

Watchdog

Counter Control Register 5

Settings

Counter Constant B

Register is not used in

Watchdog mode.

Figure 3.4:

Watchdog

waveform

In

the figure each “i”

represents an interrupt