Hercules-EBX CPU User Manual V1.02

Page 55

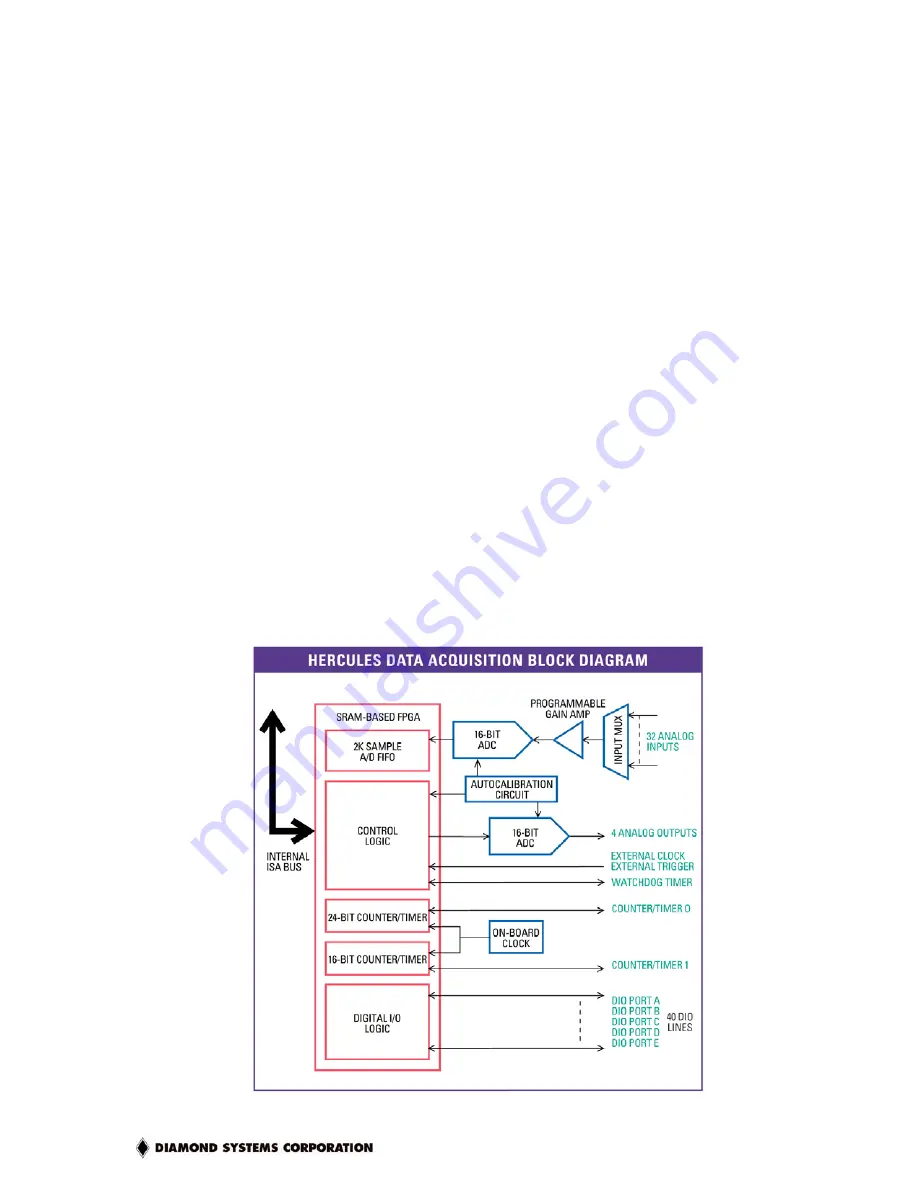

10. DATA ACQUISITION CIRCUIT – I/O MAP AND REGISTER DESCRIPTIONS

Hercules-EBX Models with Data Acquisition contain a data acquisition subsystem consisting of

A/D, D/A, digital I/O, and counter/timer features. This subsystem is equivalent to a complete add-

on data acquisition module.

The A/D section includes a 16-bit A/D converter, 32 input channels, and a 2048-sample (4kByte)

FIFO. Input ranges are programmable, and the maximum sampling rate is 250 KHz. The D/A

section includes 4 12-bit D/A channels. The digital I/O section includes 40 lines with

programmable direction. The counter/timer section includes a 24-bit counter/timer to control A/D

sampling rates and a 16-bit counter/timer for user applications. A 4-channel PWM controller is

built in to provide a method to automatically generate PWM-based waveforms.

High-speed A/D sampling is supported with interrupts and a FIFO. The FIFO is used to store a

user-selected number of samples, and the interrupt occurs when the FIFO reaches this threshold.

Once the interrupt occurs, an interrupt routine runs and reads the data out of the FIFO. In this way

the interrupt rate is reduced by a factor equal to the size of the FIFO threshold, enabling a faster

A/D sampling rate. In DOS or similar low-overhead operating systems the circuit can operate at

sampling rates of up to 250 KHz.

Note that the interrupt rate when using high sample-rates is kept low due to the large FIFO buffer.

With a 250 kHz sampling rate and a FIFO threshold of 1024 samples (half-full), the interrupt rate

is kept to a reasonable range of roughly 250Hz. Reducing the FIFO interrupt threshold will

increase the interrupt rate for a given sampling frequency, while increasing the threshold

(especially to FIFO full) will increase the risk that samples might be lost due to interrupt latency.

This rate will be an issue under multitasking OSes such as Windows, as potential interrupt

handler latencies can become quite large. Even operating a serial port at maximum speed

(115kbaud) can tax the resources of a system's latency periods, especially when such activity is

talking place over the ISA bus (as is the case both with the serial ports and with the A/D FIFO).

An interrupt rate of above 10 KHz can be difficult to sustain in Windows without the possibility of

missing samples.

The A/D circuit uses the default settings of I/O address range 240h – 25Fh (base address 240)

and IRQ 5. The IRQ setting can be changed if needed (via jumper block J4).