Hercules-EBX CPU User Manual V1.02

Page 74

Base + 29

Read/Write

EEPROM / TrimDAC Address Register

Bit

No.

7 6 5 4 3 2 1 0

Name A7 A6 A5 A4 A3 A2 A1 A0

A7-A0

EEPROM / TrimDAC address. The EEPROM recognizes address 0 – 255 using

address bits A7 – A0. The TrimDAC recognizes addresses 0 – 7 using bits A2 – A0.

In each case remaining address bits will be ignored.

NOTE: Current implementations of FPGA/Data Acquisition storage only take

advantage of the lower 128 bytes of EEPROM data at the most. The remaining 128

bytes (addresses 128-255) are available for general use.

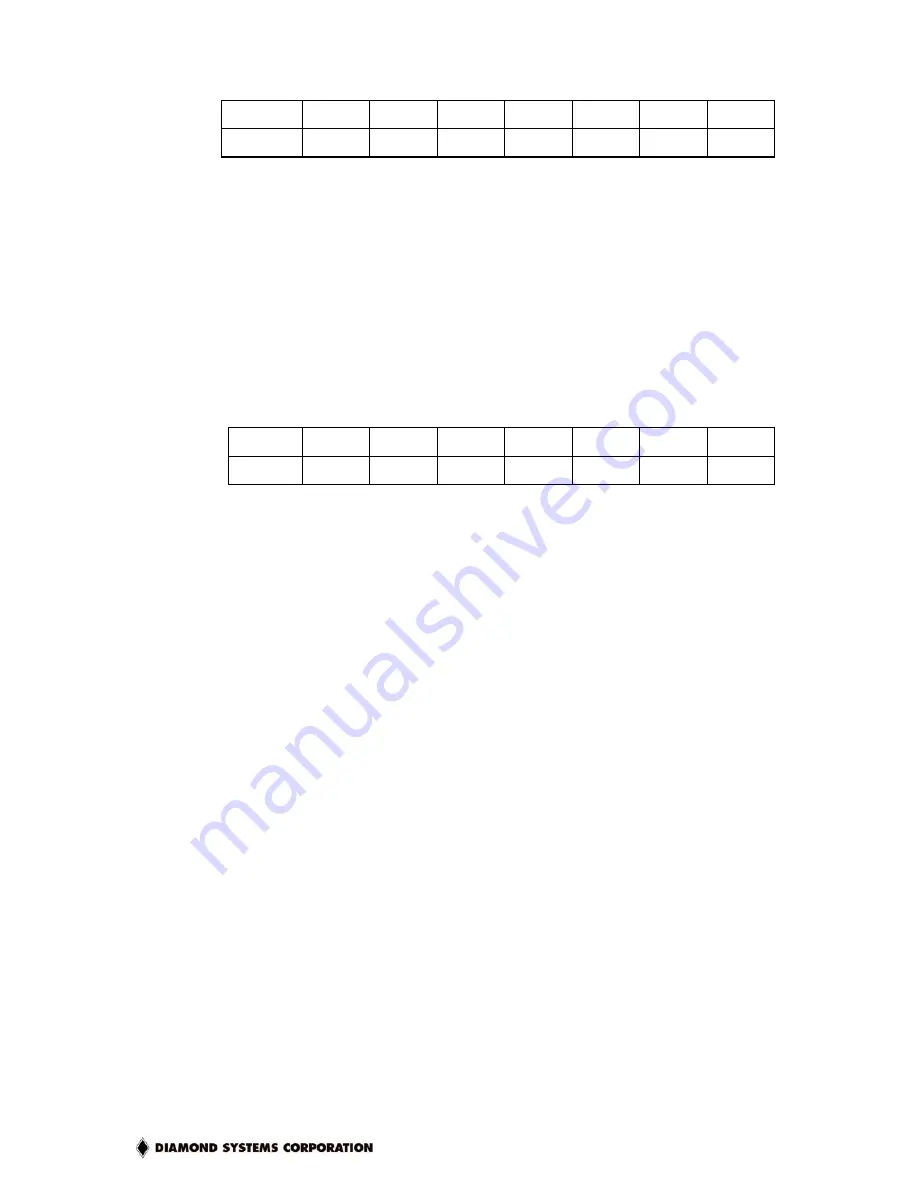

Base + 30

Write

Calibration Control Register

Bit

No.

7 6 5 4 3 2 1 0

Name

EE_EN

EE_RW

RUNCAL CMUXEN TDACEN

This register is used to initiate various commands related to autocalibration.

EE_EN

EEPROM Enable. Writing a 1 to this bit will initiate a transfer to/from the EEPROM

as indicated by the EE_RW bit. However if TDACEN is set simultaneously, EE_EN is

ignored.

EE_RW

Selects read or write operation for the EEPROM: 0 = Write, 1 = Read.

RUNCAL Writing 1 to this bit causes the board to reload the calibration settings from EEPROM

registers 0-7 into the 8 TrimDACs. This is equivalent to a “reload” operation. During

the reload operation, TDBUSY = 1.

CMUXEN Calibration multiplexer enable. The CMUXEN bit is used to enable calibration mode.

After calibration is complete, CMUXEN is reset and the desired configuration is

restored. The cal mux is used to read precision on-board reference voltages that are

used in the autocalibration process. It also can be used to read back the value of

analog output 0.

1 = enable cal mux and disable user analog input channels / muxes

0 = disable cal mux, enable user inputs

TDACEN TrimDAC Enable. Writing 1 to this bit will initiate a transfer to the TrimDAC. This bit

overrides the setting of EE_EN, so that if both bits are set simultaneously, EE_EN

will be ignored.