Chapter 8 Register Structure

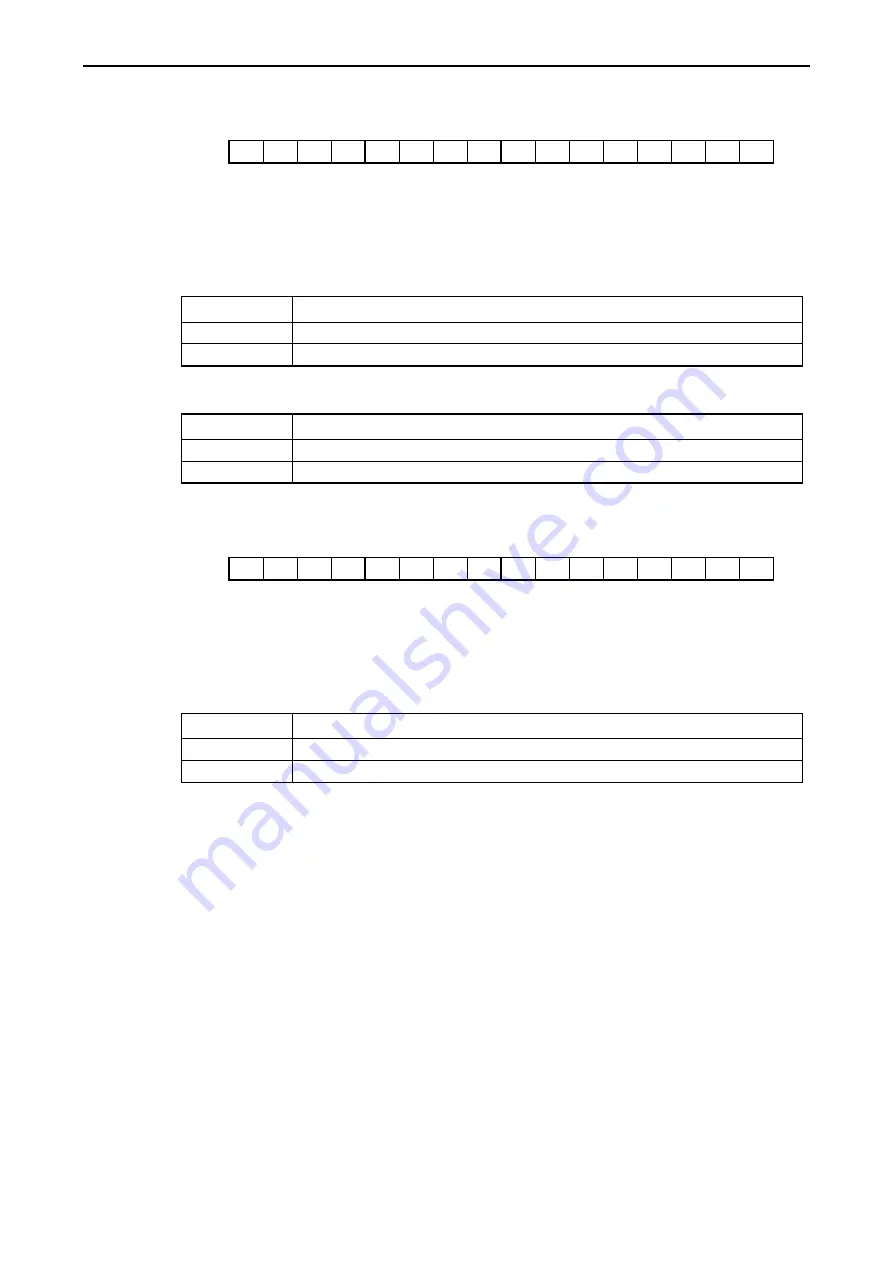

Error clear 1 control register (EC1CR)

Bit

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

+H6

- -

TEC6 TEC5 TEC4 TEC3 TEC2 TEC1

- -

OEC6 OEC5 OEC4 OEC3 OEC2 OEC1

This register is used for to clear the bits related to connection error.

Bit 15, 14, 7 and 6: Reserved

These bits are reserved bits. Please set "0" always.

Bit 13-8: STE[6:1]clear bit (TEC[6:1])

These bits request to clear Send timeout error bit (STE[6:1]) in Connection n error status register (CnESR).

Bit13-8: TEC[6:1]

Description

0

Nothing is done.

(Initial set)

1

Request to clear STE[6:1] bits.

Bit 5-0: OE[6:1] clear bit (OEC[6:1])

These bits request to clear Open error bit (OE[6:1]) in Connection n error status register.

Bit5-0: OEC[6:1]

Description

0

Nothing is done.

(Initial set)

1

Request to clear OE[6:1] bits.

Error clear 2 control register (EC2CR)

Bit

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

+H7

- -

RAC6 RAC5 RAC4 RAC3 RAC2 RAC1

- - - - - - - -

This register is used for to clear the bits related to connection error.

Bit 15, 14, 7 and 6: Reserved

These bits are reserved bits. Please set "0" always.

Bit 13-8: RAE[6:1]clear bit (RAC[6:1])

These bits request to clear Send timeout error bit (RAE[6:1]) in Connection n error status register (CnESR).

Bit13-8: RAC[6:1]

Description

0

Nothing is done.

(Initial set)

1

Request to clear RAE[6:1] bits.

Bit 5-0: Reserved

These bits are reserved bits. Please set "0" always.

8-10