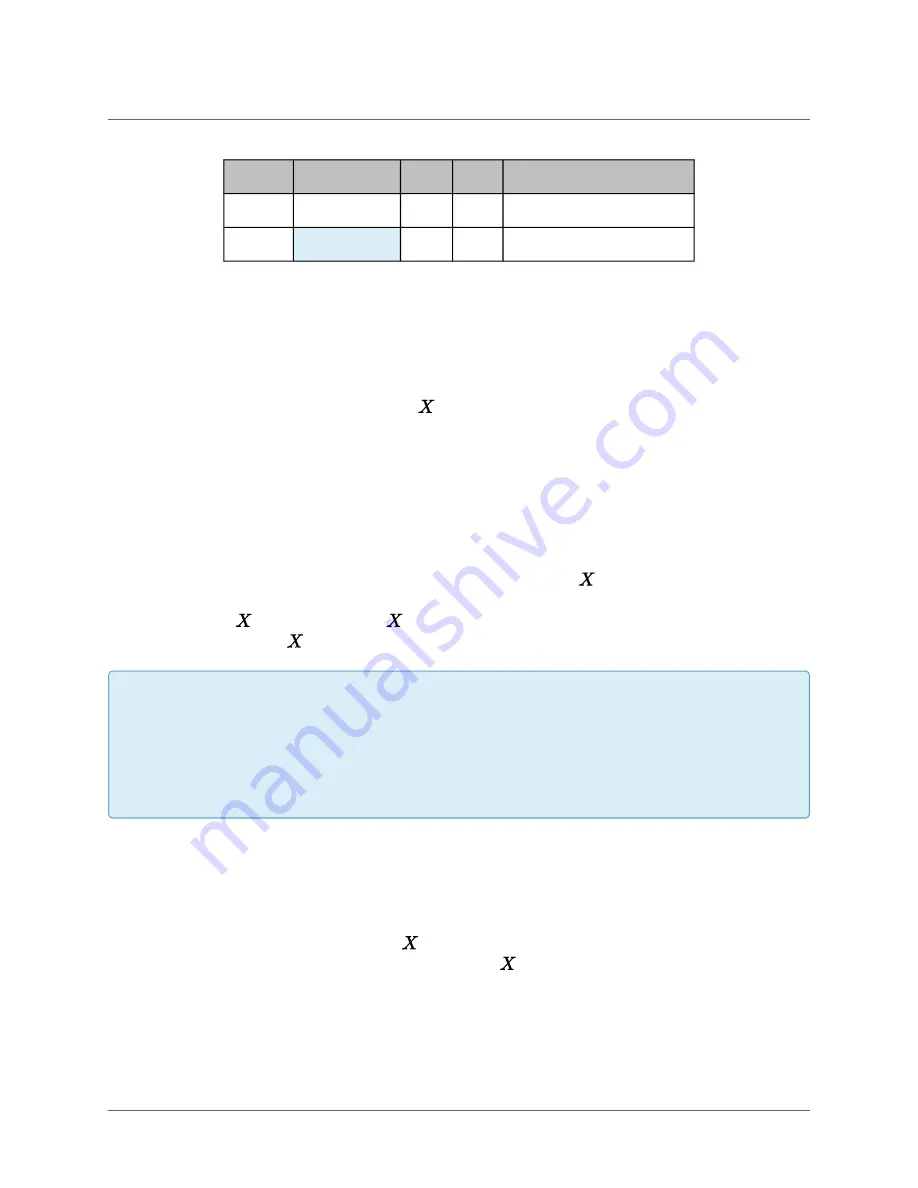

Bits

Field Name

Attr.

Rst.

Description

[15:0]

pwmcmp3

RW

X

PWM 3 Compare Value

[31:16]

Reserved

The primary use of the

ncmp

PWM compare registers is to define the edges of the PWM wave-

forms within the PWM cycle.

Each compare register is a

cmpwdith

-bit value against which the current

pwms

value is com-

pared every cycle. The output of each comparator is high whenever the value of

pwms

is greater

than or equal to the corresponding

pwmcmp

.

If the

pwmzerocomp

bit is set, when

pwms

reaches or exceeds

pwmcmp0

,

pwmcount

is cleared to

zero and the current PWM cycle is completed. Otherwise, the counter is allowed to wrap

around.

19.8

Deglitch and Sticky Circuitry

To avoid glitches in the PWM waveforms when changing

pwmcmp

register values, the

pwmdeglitch

bit in

pwmcfg

can be set to capture any high output of a PWM comparator in a

sticky bit (

pwmcmp

ip

for comparator

) and prevent the output falling again within the same

PWM cycle. The

pwmcmp

ip

bits are only allowed to change at the start of the next PWM cycle.

Note

The

pwmcmp0ip

bit will only be high for one cycle when

pwmdeglitch

and

pwmzerocmp

are

set where

pwmcmp0

is used to define the PWM cycle, but can be used as a regular PWM

edge otherwise.

If

pwmdeglitch

is set, but

pwmzerocmp

is clear, the deglitch circuit is still operational but is now

triggered when

pwms

contains all 1s and will cause a carry out of the high bit of the

pwms

incre-

menter just before the counter wraps to zero.

The

pwmsticky

bit disallows the

pwmcmp

ip

registers from clearing if they are already set and

is used to ensure interrupts are seen from the

pwmcmp

ip

bits.

Table 90:

PWM 3 Compare Register

Chapter 19 Pulse Width Modulator (PWM)

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 100