17.5

Receive Data Register (

rxdata

)

Reading the

rxdata

register dequeues a character from the receive FIFO and returns the value

in the

data

field. The

empty

flag indicates if the receive FIFO was empty; when set, the

data

field does not contain a valid character. Writes to

rxdata

are ignored.

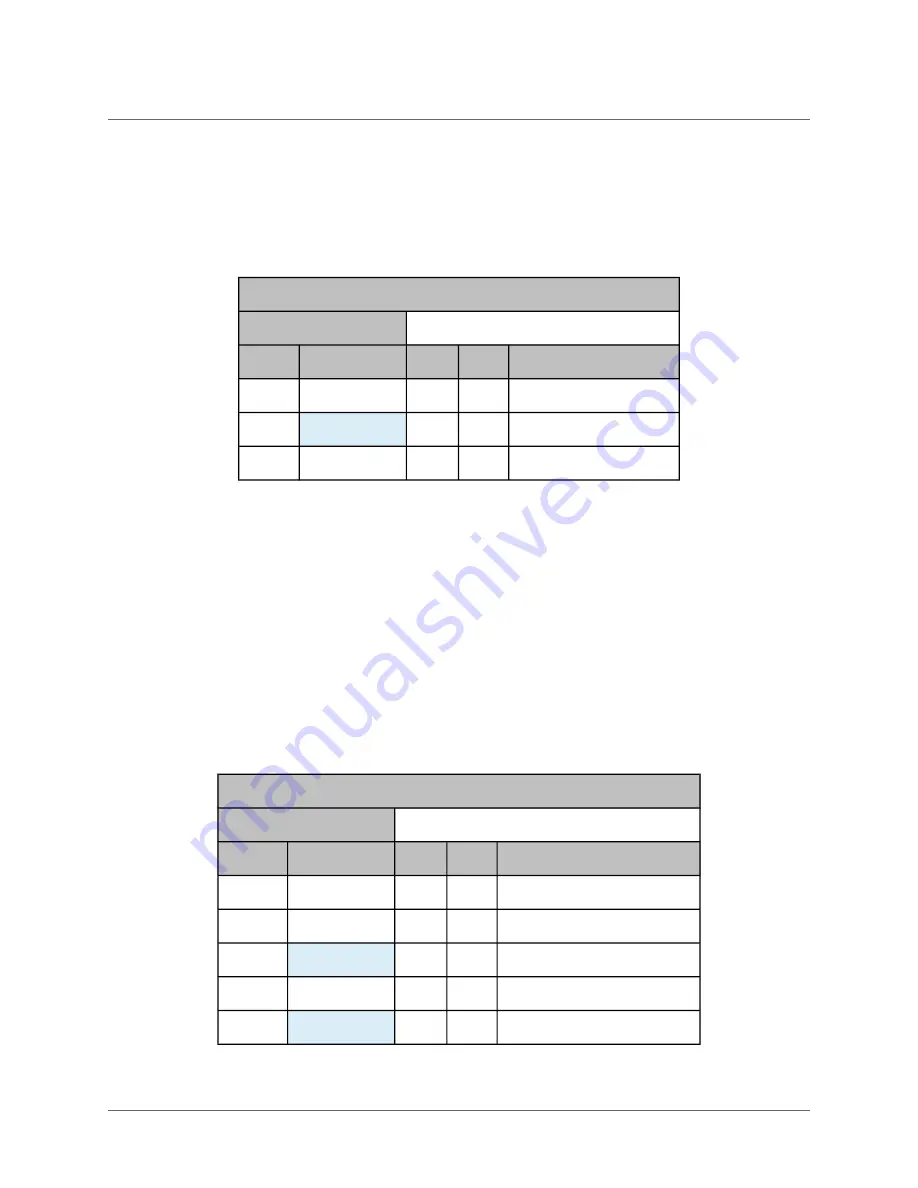

Receive Data Register (

rxdata

)

Register Offset

0x4

Bits

Field Name

Attr.

Rst.

Description

[7:0]

data

RO

X

Received data

[30:8]

Reserved

31

empty

RO

X

Receive FIFO empty

17.6

Transmit Control Register (

txctrl

)

The read-write

txctrl

register controls the operation of the transmit channel. The

txen

bit con-

trols whether the Tx channel is active. When cleared, transmission of Tx FIFO contents is sup-

pressed, and the

txd

pin is driven high.

The

nstop

field specifies the number of stop bits:

0

for one stop bit and

1

for two stop bits.

The

txcnt

field specifies the threshold at which the Tx FIFO watermark interrupt triggers.

The

txctrl

register is reset to

0

.

Transmit Control Register (

txctrl

)

Register Offset

0x8

Bits

Field Name

Attr.

Rst.

Description

0

txen

RW

0x0

Transmit enable

1

nstop

RW

0x0

Number of stop bits

[15:2]

Reserved

[18:16]

txcnt

RW

0x0

Transmit watermark level

[31:19]

Reserved

Table 51:

Receive Data Register

Table 52:

Transmit Control Register

Chapter 17 Universal Asynchronous Receiver/Transmitter

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 78