Chapter 2

List of Abbreviations and Terms

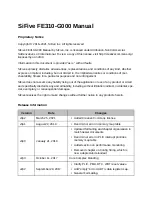

Term

Definition

BHT

Branch History Table

BTB

Branch Target Buffer

RAS

Return-Address Stack

CLINT

Core-Local Interruptor. Generates per-hart software interrupts and timer

interrupts.

CLIC

Core-Local Interrupt Controller. Configures priorities and levels for core

local interrupts.

hart

HARdware Thread

DTIM

Data Tightly Integrated Memory

ITIM

Instruction Tightly Integrated Memory

JTAG

Joint Test Action Group

LIM

Loosely Integrated Memory. Used to describe memory space delivered in

a SiFive Core Complex but not tightly integrated to a CPU core.

PMP

Physical Memory Protection

PLIC

Platform-Level Interrupt Controller. The global interrupt controller in a

RISC-V system.

TileLink

A free and open interconnect standard originally developed at UC Berke-

ley.

RO

Used to describe a Read Only register field.

RW

Used to describe a Read/Write register field.

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 13