14.1

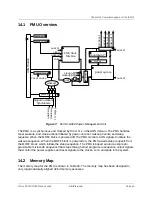

PMU Overview

pmui e

d

w

a

k

e

u

p

a

w

a

k

e

u

p

p

m

u

_

o

u

t

_

0

h

f

c

l

k

r

s

t

c

o

r

e

r

s

t

r

t

c

c

m

p

i

p

pmupr ogr am

pmucause

A

O

N

T

ile

L

in

k

pmukey

Signal Condition/

Synchronize

r eset cause

p

m

u

u

p

c

+1

sleep µPC

wakeup µPC

del ay

Countdown 2

N

end?

PMU State

Machine

aonr st

aonr st

pmusl eep

wakeup?

aonr st

sleep

wakeup

done

p

m

u

_

o

u

t

_

1

Figure 7:

FE310-G000 Power-Management Unit

The PMU is a synchronous unit clocked by the

lfClk

in the AON domain. The PMU handles

reset, wakeup, and sleep actions initiated by power-on reset, wakeup events, and sleep

requests. When the MOFF block is powered off, the PMU monitors AON signals to initiate the

wakeup sequence. When the MOFF block is powered on, the PMU awaits sleep requests from

the MOFF block, which initiate the sleep sequence. The PMU is based around a simple pro-

grammable microcode sequencer that steps through short programs to sequence output signals

that control the power supplies and reset signals to the clocks, core, and pads in the system.

14.2

Memory Map

The memory map for the PMU is shown in Table 34. The memory map has been designed to

only require naturally aligned 32-bit memory accesses.

Chapter 14 Power-Management Unit (PMU)

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 63