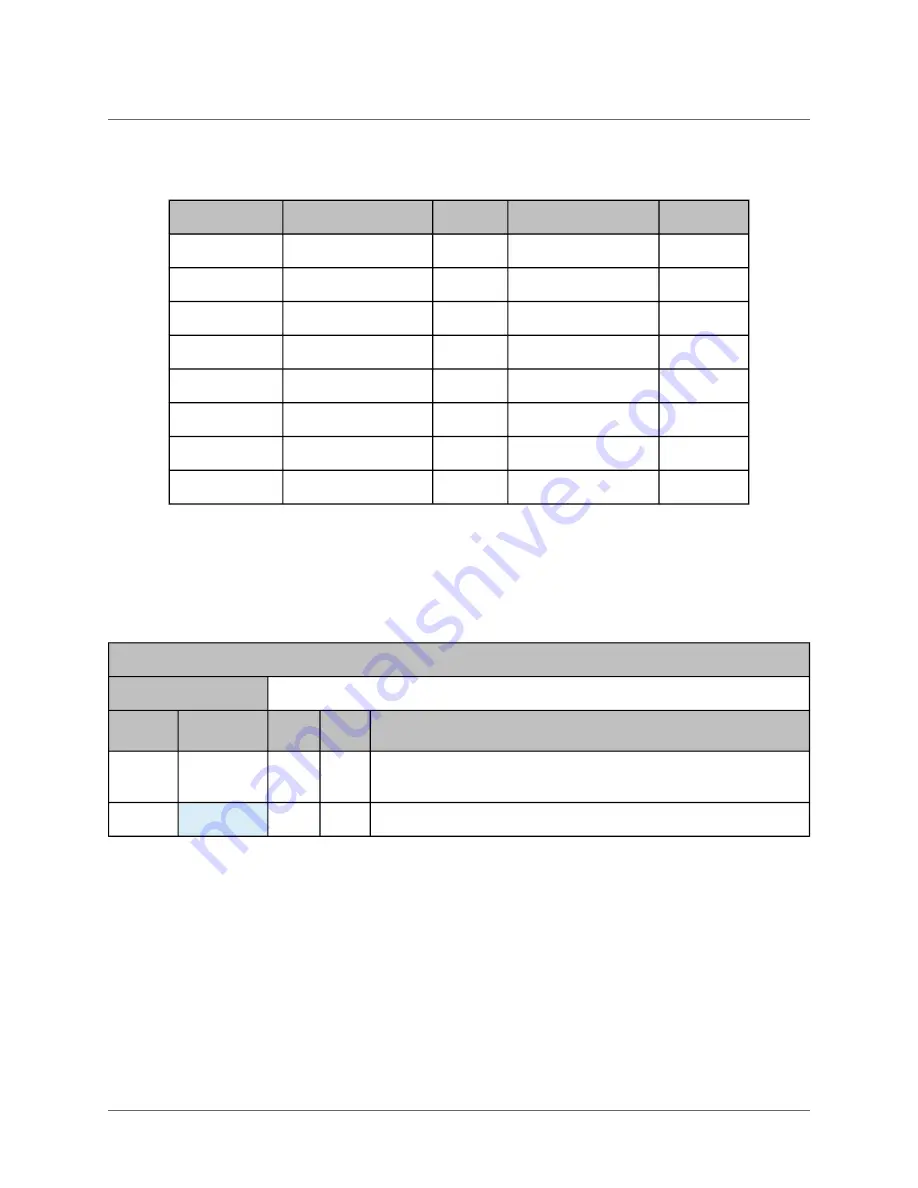

Table 56:

Common baud rates (MIDI=31250, DMX=250000) and required

divide values to achieve them with given bus clock frequencies. The divide val-

ues are one greater than the value stored in the

div

register.

tlclk

(MHz)

Target Baud (Hz)

Divisor

Actual Baud (Hz)

Error (%)

200

31250

6400

31250

0

200

115200

1736

115207

0.0064

200

250000

800

250000

0

200

1843200

109

1834862

0.45

384

31250

12288

31250

0

384

115200

3333

115211

0.01

384

250000

1536

250000

0

384

1843200

208

1846153

0.16

The receive channel is sampled at 16× the baud rate, and a majority vote over 3 neighboring

bits is used to determine the received value. For this reason, the divisor must be ≥16 for a

receive channel.

Baud Rate Divisor Register (

div

)

Register Offset

0x18

Bits

Field

Name

Attr.

Rst.

Description

[15:0]

div

RW

X

Baud rate divisor.

div_width

bits wide, and the reset

value is

div_init

.

[31:16]

Reserved

Table 57:

Baud Rate Divisor Register

Chapter 17 Universal Asynchronous Receiver/Transmitter

SiFive FE310-G000 Manual: v3p2

© SiFive, Inc.

Page 81