ADV7181B

Rev. B | Page 38 of 100

SYNCHRONIZATION OUTPUT SIGNALS

HS Configuration

The following controls allow the user to configure the behavior

of the HS output pin only:

•

Beginning of HS signal via HSB[10:0]

•

End of HS signal via HSE[10:0]

•

Polarity of HS using PHS

The HS begin and HS end registers allow the user to freely

position the HS output (pin) within the video line. The values

in HSB[10:0] and HSE[10:0] are measured in pixel units from

the falling edge of HS. Using both values, the user can program

both the position and length of the HS output signal.

HSB[10:0] HS Begin, Address 0x34[6:4],

Address 0x35[7:0]

The position of this edge is controlled by placing a binary

number into HSB[10:0]. The number applied offsets the edge

with respect to an internal counter that is reset to 0 immediately

after EAV Code FF, 00, 00, XY (see Figure 19). HSB is set to

00000000010b, which is 2 LLC1 clock cycles from Count[0].

The default value of HSB[10:0] is 0x002, indicating that the HS

pulse starts two pixels after the falling edge of HS.

HSE[10:0] HS End, Address 0x34[2:0], Address 0x36[7:0]

The position of this edge is controlled by placing a binary

number into HSE[10:0]. The number applied offsets the edge

with respect to an internal counter that is reset to 0 immediately

after EAV Code FF, 00, 00, XY (see Figure 19). HSE is set to

00000000000b, which is 0 LLC1 clock cycles from Count[0].

The default value of HSE[10:0] is 000, indicating that the HS

pulse ends zero pixels after a falling edge of HS.

For example

1.

To shift the HS toward active video by 20 LLC1s, add

20 LLC1s to both HSB and HSE, that is, HSB[10:0] =

[00000010110], HSE[10:0] = [00000010100].

2.

To shift the HS away from active video by 20 LLC1s, add

1696 LLC1s to both HSB and HSE (for NTSC), that is,

HSB[10:0] = [11010100010], HSE[10:0] = [11010100000].

1696 is derived from the NTSC total number of pixels =

1716.

To move 20 LLC1s away from active video is equal to subtracting

20 from 1716 and adding the result in binary to both HSB[10:0]

and HSE[10:0].

PHS Polarity HS, Address 0x37[7]

The polarity of the HS pin can be inverted using the PHS bit.

When PHS is 0 (default), HS is active high.

When PHS is 1, HS is active low.

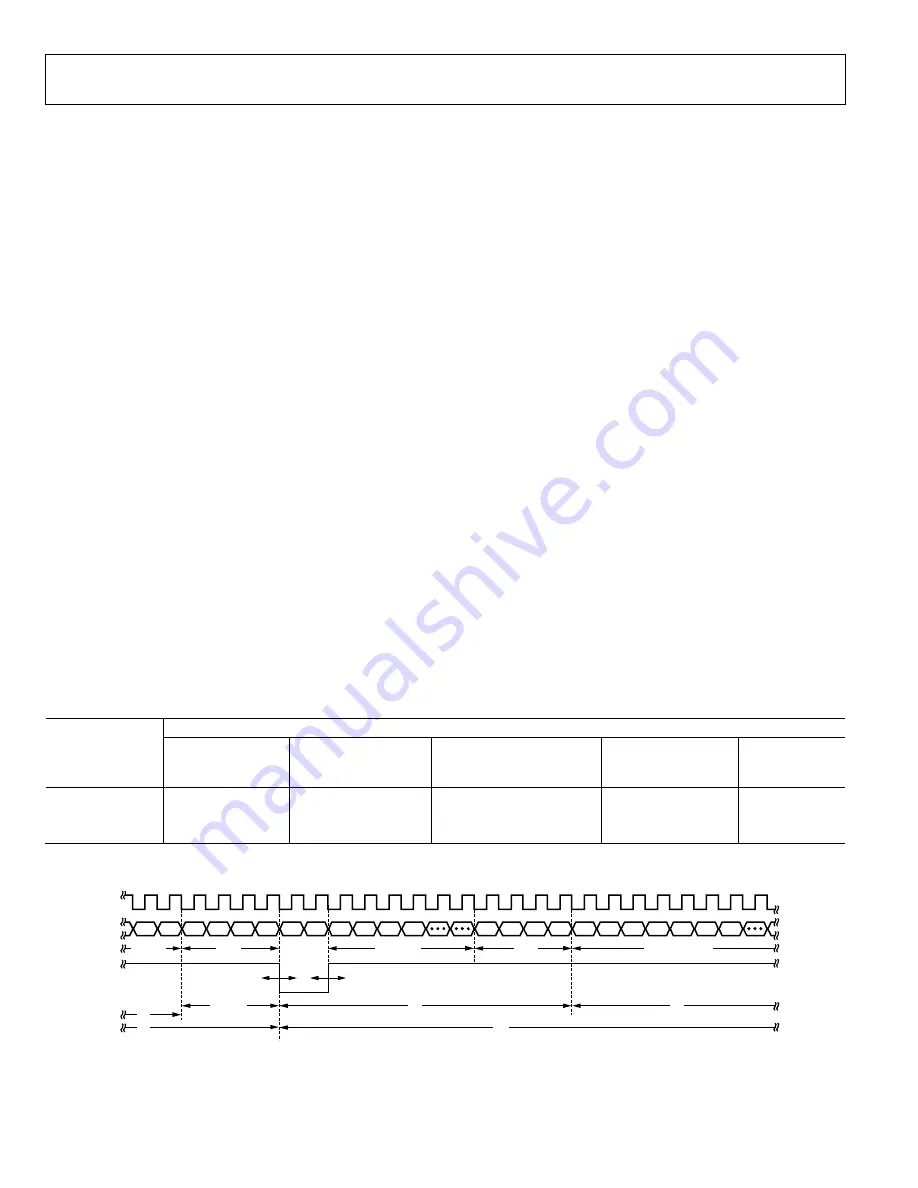

Table 54. HS Timing Parameters (see Figure 19)

Characteristic

Standard

HS Begin Adjust

(HSB[10:0])

(Default)

HS End Adjust

(HSE[10:0])

(Default)

HS to Active Video

(LLC1 Clock Cycles)

(C in Figure 19) (Default)

Active Video

Samples/Line

(D in Figure 19)

Total LLC1

Clock Cycles

(E in Figure 19)

NTSC

00000000010b

00000000000b

272

720Y + 720C = 1440

1716

NTSC Square Pixel

00000000010b

00000000000b

276

640Y + 640C = 1280

1560

PAL

00000000010b

00000000000b

284

720Y + 720C = 1440

1728

E

ACTIVE

VIDEO

LLC1

PIXEL

BUS

HS

Cr

Y

FF

00

00

XY

80

10

80

10

80

10

FF

00

00

XY

Cb

Y

Cr

Y

Cb

Y

Cr

4 LLC1

D

HSB[10:0]

HSE[10:0]

C

E

D

SAV

ACTIVE VIDEO

H BLANK

EAV

04984-019

Figure 19. HS Timing