338

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

Digital Blocks

Timers may be chained in 8-bit lengths up to 32 bits.

17.1.6.1

Usability Exceptions

The following are usability exceptions for the Timer function:

1. Capture operation is not supported at 48 MHz.

2. DR2 is not writeable when the Timer is enabled.

3. CR1 is not writeable when the Timer is enabled.

17.1.6.2

Block Interrupt

The Timer block has a selection of four interrupt sources.

Interrupt on Terminal Count (TC) and Interrupt on Compare

may be selected in Mode bit 0 of the function register. The

third interrupt source, Interrupt on Capture, may be selected

with the Capture Interrupt bit in the control register.

■

Interrupt on Terminal Count

: The positive edge of ter-

minal count (primary output) generates an interrupt for

this block. The timing of the interrupt follows the TC

pulse width setting in the control register.

■

Interrupt on Compare

: The positive edge of compare

(auxiliary output) generates an interrupt for this block.

■

Interrupt on Capture

: Hardware or software capture

generates an interrupt for this block. The interrupt occurs

at the closing of the DR2 latch on capture.

■

Interrupt on KILL

: The interrupt occurs when KILL is

asserted.

17.1.7

Counter Function

A Counter consists of a period register, a synchronous down

counter, and a compare register. The Counter function is

identical to the Timer function, with the following exceptions:

■

The data input is a counter gate (enable), rather than a

capture input. Counters do not implement synchronous

capture. The DR0 register in a counter should not be

read when it is enabled.

■

The compare output is the primary output and the Termi-

nal Count (TC) is the auxiliary output (opposite of the

Timer).

■

Terminal count output is full cycle only.

When the counter is disabled and a period value is written

into DR1, the period value is also loaded into DR0. When

the counter is enabled, the counter counts down until termi-

nal count (a count of 00h) is reached. On the next clock

edge, the period is reloaded and, on subsequent clocks,

counting continues. (Refer to the timing diagram for this

function on page

17.1.7.1

Counter Timing

This function also supports multi-shot mode. When the

multi-shot register is set to non-zero, the function is in multi-

shot mode. For example, if the multi-shot register is set to

01h, the function is disabled after it reaches the first 00

value in DR0. If the multi-shot register is set to 02h, when

the function reaches the first 00, DR0 reloads and runs

again. The function is disabled after the second 00 in DR0

register. The multi-shot supports up to the MAX number of

15 shots.

The counter implements a compare function between DR0

and DR2. The Compare signal is the primary function out-

put. Mode bit 1 sets the compare type (DR0 <= DR2 or DR0

< DR2) and Mode bit 0 sets the interrupt type (terminal count

or compare). Note that in default if you write to DR2 in func-

tion running state, DR2 data changes immediately and then

the compare output may change immediately after. A config-

uration bit in CR0[1] can be used to delay the DR2 data

changing until TC occurs (that is, at DR0 reloading). There-

fore unusual changes will not be seen on compare out after

changing the DR2 data.

There is another mode, called NPS mode, supported at the

compare output. When it is set, the compare output is

delayed half clock cycle. It is used to achieve a higher reso-

lution when 48 MHz clock is used as block clock.

This function also supports KILL function. There are two

KILL modes: KILL-Disable and KILL-Reload. In KILL-Dis-

able mode, the function is disabled immediately when kill is

asserted. The function must be restarted in firmware. In

KILL-Reload mode, the DR0 register and multi-shot counter

register stays in reload state when KILL is high, and the

function counts down when KILL is released. The function

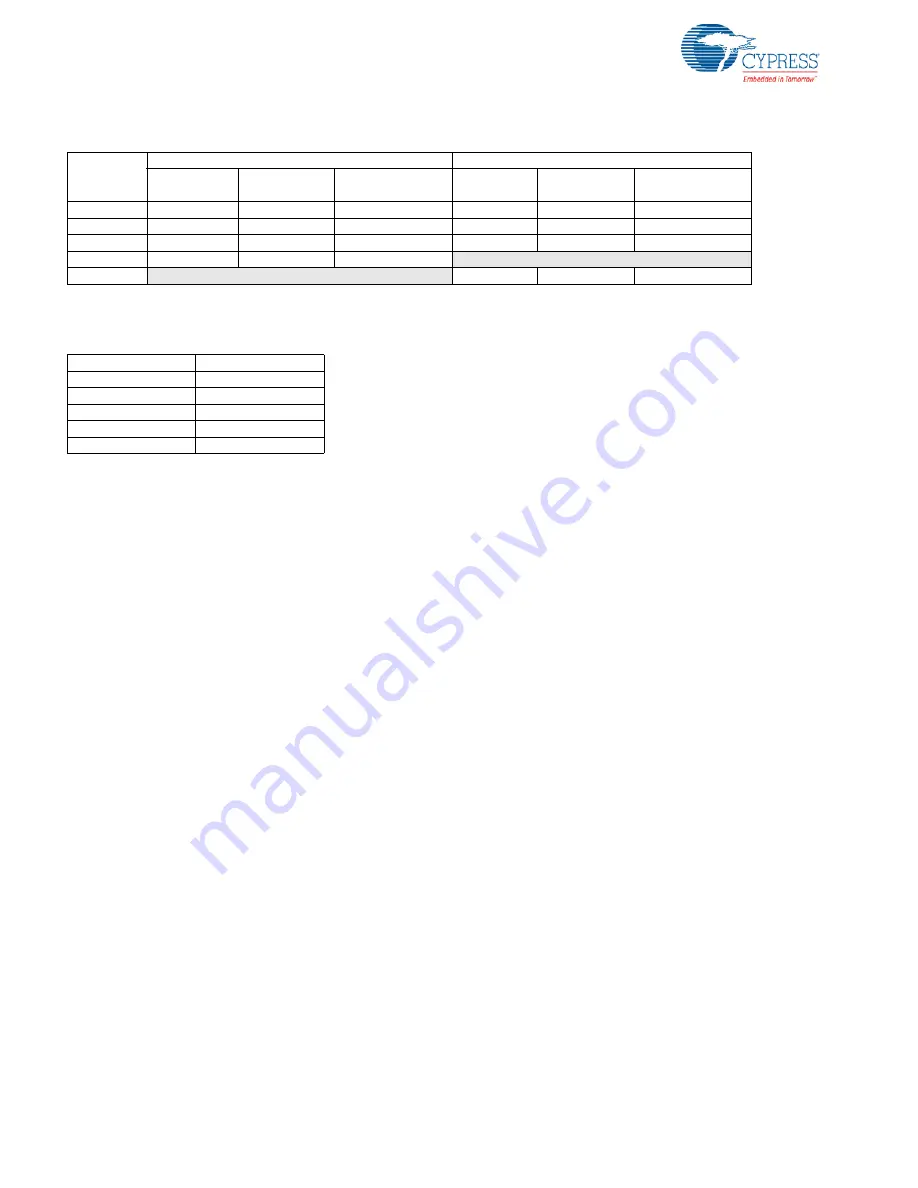

Table 17-2. Timer Interrupt Source

Interrupt

Source

Non Multi-shot Mode

Multi-shot Mode

KILL_INT

(CR1[0])

Capture INT

(CR0[1])

Compare True

(FN[1])

KILL_INT

(CR1[0])

Capture INT

(CR0[1])

Compare True

(FN[1])

KILL

1

*

*

1

*

*

Capture

0

1

*

0

1

*

Compare

0

0

1

0

0

1

TC

0

0

0

Last-Shot

0

0

0

Table 17-3. Timer Control Signals in Chained Block

Item

Configured in

Capture

LSB Block

KILL

LSB Block

Multi-shot Period

MSB Block

Clock

All chained Blocks

KILL Mode

All chained Blocks

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...