544

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

10-Bit SAR ADC Controller

35.3.9

SADC_CR2

The 10-bit SAR ADC controller only exists in the

CY8C28x03, CY8C28x13, CY8C28x33, CY8C28x43, and

CY8C28x45 PSoC devices.

Bit 7: REFSEL.

1 to select external Vref other than Vdd.

EXTREF in SADC_CR4 for external ref selection

Bit 6: BUFEN.

1 to enable Vref buffer. Otherwise bypasses

Vref buffer.

Bit 5: VDBEN.

1 to enable voltage doubler in ADC compar-

ator.

Bit 4: VDB_CLKSEL.

1 to select SYSLCK as VDB clock.

Otherwise select SYSCLK/4 as VDB clock.

Bit 3: FREERUN.

1 is ADC in FREERUN mode if ADC is

not in auto-align mode.

For additional information, refer to the

35.3.10

SADC_CR3

The 10-bit SAR ADC controller only exists in the

CY8C28x03, CY8C28x13, CY8C28x33, CY8C28x43, and

CY8C28x45 PSoC devices.

Bit 7: LALIGN:

‘1’ to left justified data format.

Bits 2 to 0: ADC_TRIM0[2:0].

Sent to ADC comparator

block directly. The reset value is 100b.

For additional information, refer to the

35.3.11

SADC_CR4

10-bit SAR ADC controller only exists in the CY8C28x03,

CY8C28x13, CY8C28x33, CY8C28x43, and CY8C28x45

PSoC devices.

Bit 7: EXTREF.

‘1’ to select external Vref input on P2[5].

For additional information, refer to the

35.4

PSoC Device Distinctions

The 10-bit SAR ADC controller only exists in the

CY8C28x03, CY8C28x13, CY8C28x33, CY8C28x43, and

CY8C28x45 PSoC device groups.

35.5

Clocking

SYSCLK is a primary clock input of SAR ADC controller

block.

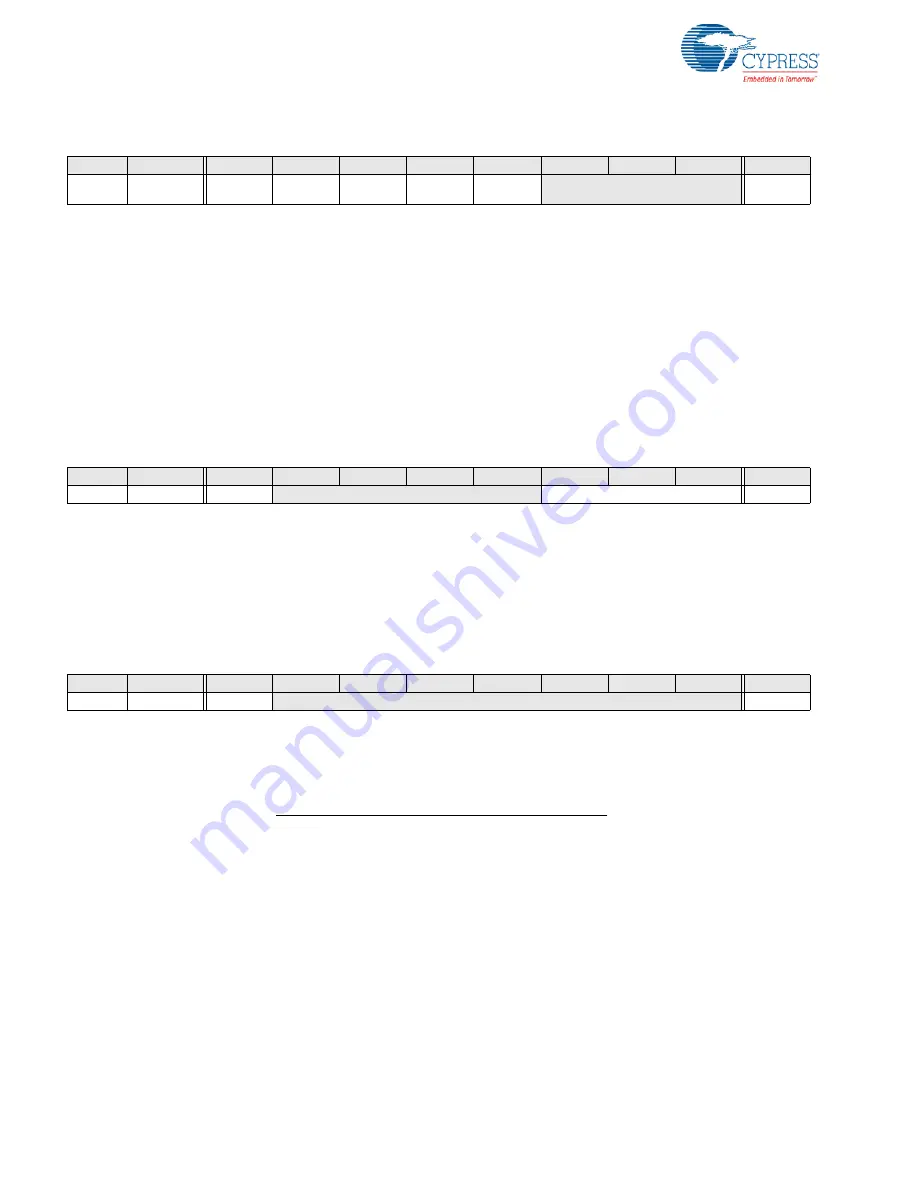

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

1,AAh

REFSEL

BUFEN

VDBEN

VDB_CLKS

EL

FREERUN

RW : 00

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

1,ABh

LALIGN

ADC_TRIM0[2:0]

RW : 04h

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

1,ACh

EXTREF

# : 02h

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...