344

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

Digital Blocks

17.1.12

SPI Master Function

The SPI Master (SPIM) offers SPI operating modes 0-3. By

default, the MSb of the data byte is shifted out first. An addi-

tional option can be set to reverse the direction and shift the

data byte out LSb first. (Refer to the timing diagrams for this

function on page

When configured for SPIM, DR0 functions as a shift register,

with input from the DATA input (MISO) and output to the pri-

mary output F1 (MOSI). DR1 is the TX Buffer register and

DR2 is the RX Buffer register.

The SPI protocol requires data to be registered at the device

input, on the opposite edge of the clock that operates the

output shifter. An additional register (RXD), at the input to

the DR0 shift register, has been implemented for this pur-

pose. This register stores received data for one-half cycle,

before it is clocked into the shift register.

The SPIM controls

between master and

slave, because it generates the bit clock for internal clocking

and for clocking the SPIS. The bit clock is derived from the

CLK input selection. Because the PSoC system clock gener-

ators produce clocks with varying duty cycles, the SPIM

divides the input CLK by two to produce a bit clock with a 50

percent duty cycle. This clock is gated, to provide the SCLK

output on the auxiliary output, during byte transmissions.

There are four control bits and four status bits in the control

register that provide for PSoC device interfacing and syn-

chronization.

The SPIM hardware has no support for driving the Slave

Select (SS_) signal. The behavior and use of this signal is

application and PSoC device dependent and, if required,

must be implemented in firmware.

SPIM supports variable length from 8 bits to 16 bits. Two

adjacent communication blocks are able to be chained

together to achieve MAX 16-bit SPI. Note the last DCC block

in one row can be chained with the first DCC block in next

row.

shows the configurations in different length

requirement. Note that the same clock setting should be

used in both blocks. And the SPI output comes from LSB

Block and SPI input goes to MSB block if LSB first option is

set. Otherwise SPI output comes from MSB block and SPI

input goes to LSB block.

17.1.12.1

Usability Exceptions

The following are usability exceptions for the SPI Protocol

function:

1. The MISO input must be resynchronized at the row

inputs.

2. The DR2 (Rx Buffer) register is not writeable.

3. CR1 is not writeable when the SPIM is enabled.

17.1.12.2

Block Interrupt

The SPIM block has a selection of two interrupt sources:

Interrupt on TX Reg Empty (default) or interrupt on SPI

Complete. Mode bit 1 in the function register controls the

selection. These mode are discussed in detail in

.

If SPI Complete is selected as the block interrupt, the control

register must be read in the interrupt routine so that this sta-

tus bit is cleared; otherwise, no subsequent interrupts are

generated.

17.1.13

SPI Slave Function

The SPI Slave (SPIS) offers SPI operating modes 0-3. By

default, the MSb of the data byte is shifted out first. An addi-

tional option can be set to reverse the direction and shift the

data byte out LSb first. (Refer to the timing diagrams for this

function on page

When configured for SPI, DR0 functions as a shift register,

with input from the DATA input (MOSI) and output to the pri-

mary output F1 (MISO). DR1 is the TX Buffer register and

DR2 is the RX Buffer register.

The SPI protocol requires data to be registered at the device

input, on the opposite edge of the clock that operates the

output shifter. An additional register (RXD), at the input to

the DR0 shift register, is implemented for this purpose. This

register stores received data for one-half cycle before it is

clocked into the shift register.

The SPIS function derives all clocking from the SCLK input

(typically an external SPI Master). This means that the mas-

ter must initiate all transmissions. For example, to read a

byte from the SPIS, the master must send a byte.

There are four control bits and four status bits in the control

register that provide for PSoC device interfacing and syn-

chronization.

In the SPIS, there is an additional data input, Slave Select

(SS_), which is an

signal. SS_ must be asserted

to enable the SPIS to receive and transmit. SS_ has two

high level functions: 1) To allow for the selection of a given

slave in multi-slave environment, and 2) To provide addi-

tional clocking for TX data queuing in SPI modes 0 and 1.

SS_ may be controlled from an external pin through a Row

Input or can be controlled by way of user firmware.

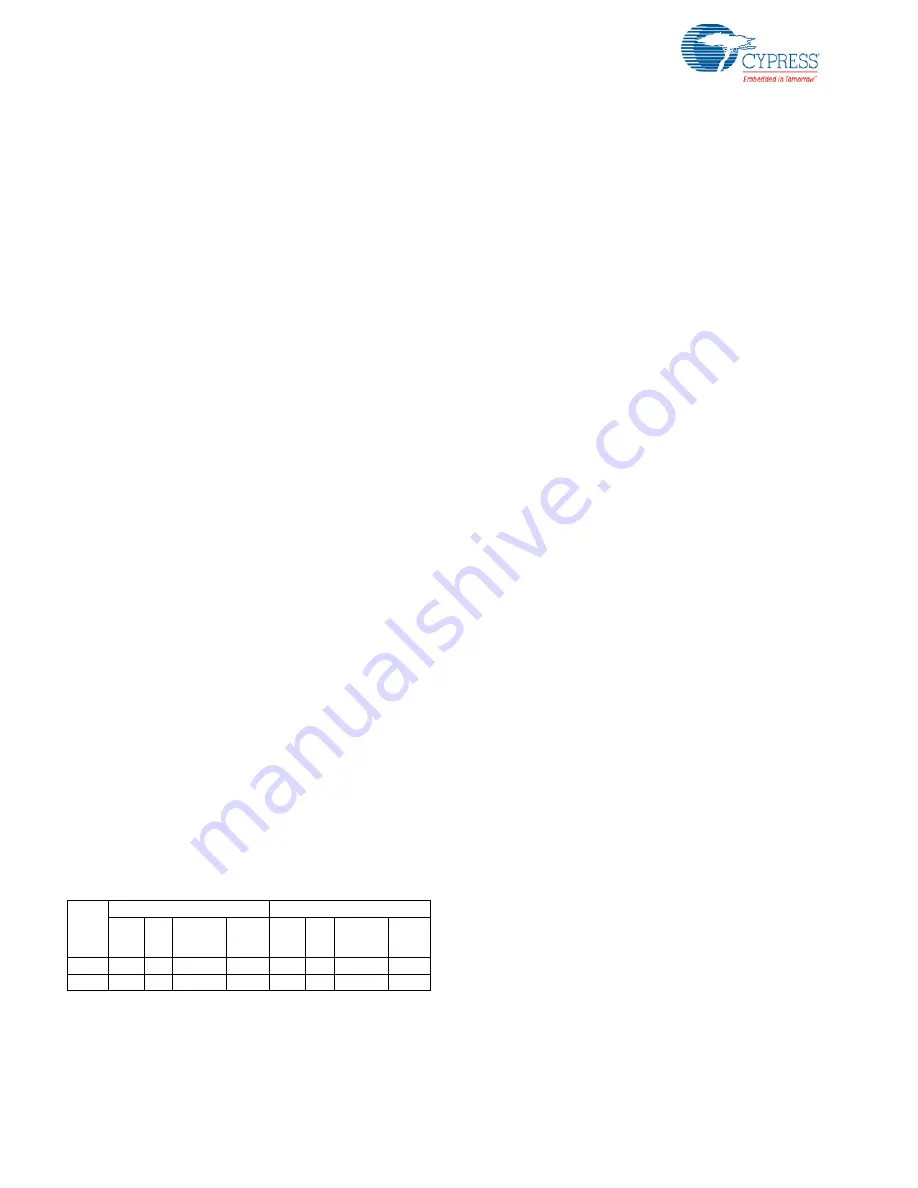

Table 17-9. Variable Length SPI Configuration

SPI

Length

MSB Block

LSB Block

Chain LSB

SPI

Length

End

Block

(in FN)

Chain LSB

SPI

Length

End

Block

(in FN)

8-bit

0

*

*

*

N/A

N/A

N/A

N/A

12-bit

1

0

5’b0_1100

1

1

1

5’b0_1100

0

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...