496

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

I

2

C

28.2.2

Master Operation

To prepare for a Master mode transaction, the PSoC device

must determine if the bus is free. This is done by polling the

BusBusy status. If busy, interrupts can be enabled to detect

a Stop condition. When it is determined that the bus is avail-

able, firmware should write the address byte into the

I2C_DR register and set the Start Gen bit in the I2C_MSCR

register.

If the slave sub-unit is not enabled, the block is in Master

Only mode. In this mode, the unit does not generate inter-

rupts or stall the I

2

C bus on externally generated Start condi-

tions.

In a multi-master environment there are two additional out-

comes possible:

1. The PSoC device was too late to reserve the bus as a

master, and another master may have generated a Start

and sent an Address/RW byte. In this case, the unit as a

master will fail to generate a Start and is forced into

Slave mode. The Start will be pending and eventually

occur at a later time when the bus becomes free. When

the interrupt occurs in Slave mode, the PSoC device can

determine that the Start command was unsuccessful by

reading the I2C_MSCR register Start bit, which is reset

on successful Start from this unit as master. If this bit is

still a ‘1’ on the Start/Address interrupt, it means that the

unit is operating in Slave mode. In this case, the data

register has the master’s address data.

2. If another master starts a transmission at the same time

as this unit, arbitration occurs. If this unit loses the arbi-

tration, the LostArb status bit is set. In this case, the

block releases the bus and switches to Slave operation.

When the Start/Address interrupt occurs, the data regis-

ter has the winning master’s address data.

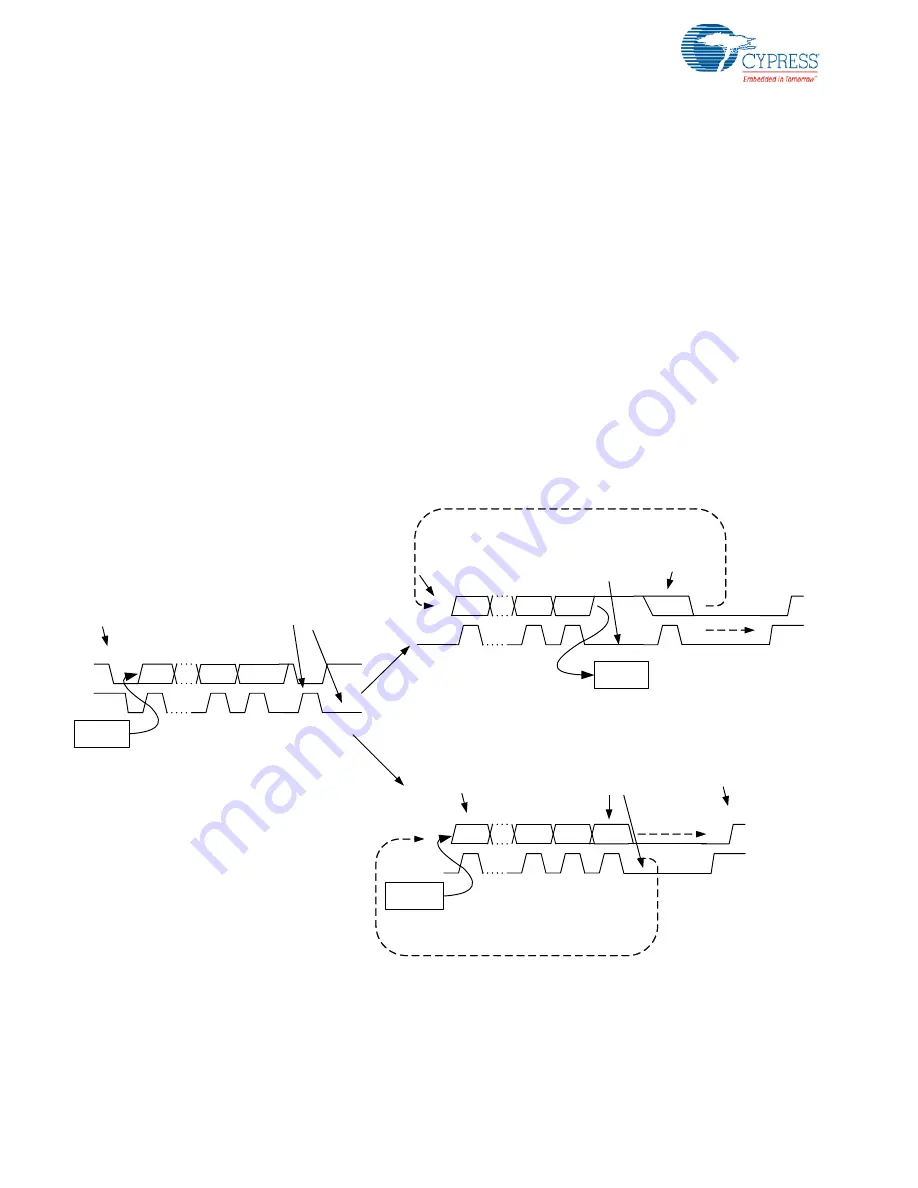

is a graphical representation of a typical data

transfer from the master perspective.

Figure 28-4. Master Operation

1

7

8

1

7

8

9

START

7-Bit Address

R/W

8-Bit Data

ACK/

NACK

STOP

A Start/Address compete

interrupt is generated.

The SCL line is held low.

1

7

8

8-Bit Data

STOP

SHIFTER

M8C writes a byte to

transmit I2C_DR

register.

9

SHIFTER

Re

ad

(R

X)

Wri

te

(T

X

)

M8C issues a

command to the

I2C_SCR register.

Master Transmitter/Receiver

ACK/

NACK

M8C issues TRANSMIT

command to the

I2C_SCR register.

M8C issues ACK/

NACK command to

the I2C_SCR

register.

M8C reads the

received byte from

I2C_DR register.

ACK = Slave

says OK to

receive more.

NACK =

Slave says no

more.

NACK = M8C

master indicates

end-of-data

ACK = M8C

master wants

more

SHIFTER

M8C writes address

byte to the I2C_DR

register.

M8C issues

Generate

START

command to

I2C_MCR.

An interrupt is generated

on completed reception

of the byte. The SCL line

is held low.

M8C issues STOP

command

Master wants

to send more

bytes.

An interrupt is generated

on completion of the byte

+ ACK/NACK. The SCL

line is held low.

9

ACK

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...