CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

511

29. Internal Voltage Reference

This chapter discusses the Internal Voltage Reference and its associated register. The internal voltage reference provides an

absolute value of 1.3 V to a variety of subsystems in the PSoC device. For a quick reference of all PSoC

®

registers in address

order, refer to the

Register Details chapter on page 125

.

29.1

Architectural Description

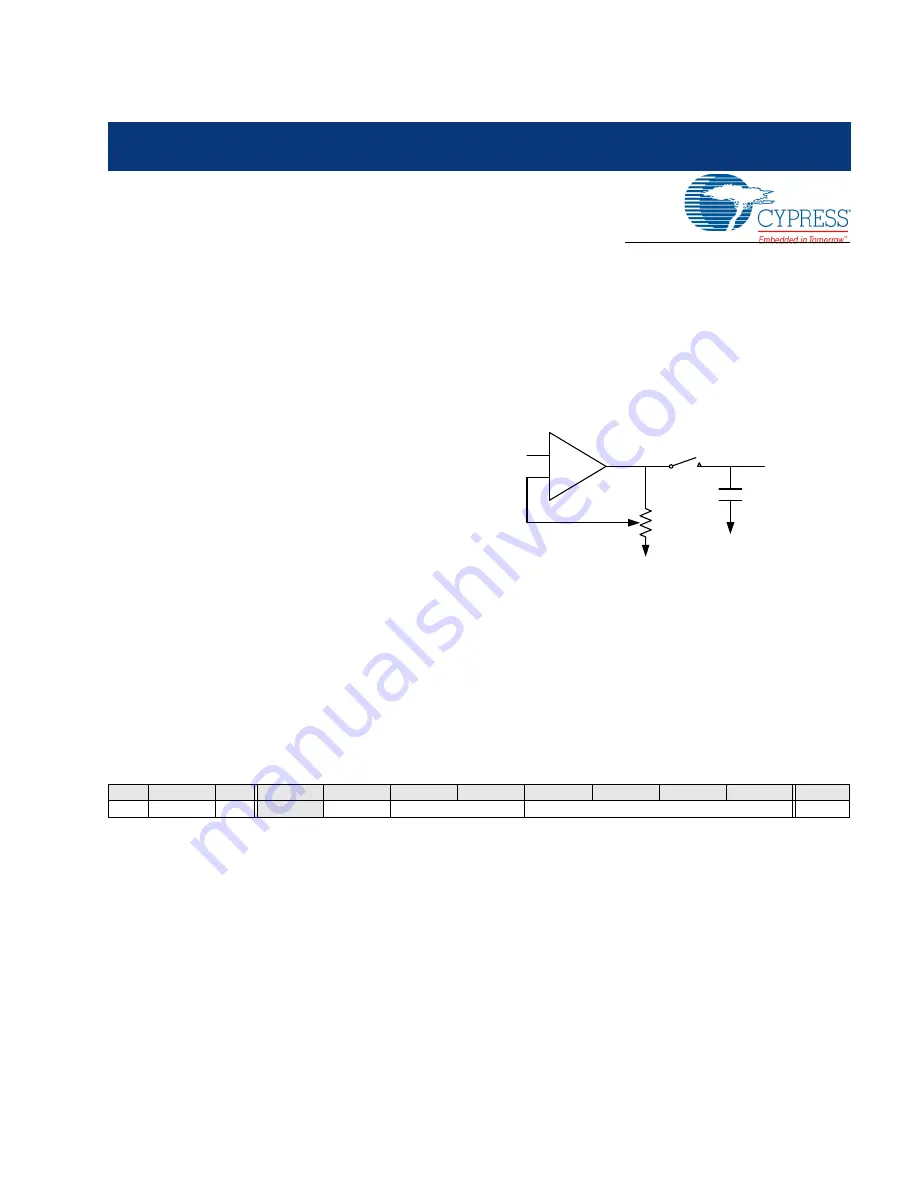

The Internal Voltage Reference is made up of two blocks: a

bandgap voltage generator and a buffer with sample and

hold. The bandgap voltage generator is a typical (V

BE

+ K

V

T

) design.

The buffer circuit provides gain to the 1.20 V bandgap volt-

age, to produce a 1.30 V reference. A simplified

is illustrated in

. The connection between ampli-

fier and capacitor is made through a CMOS switch, allowing

the reference voltage to be used by the system while the ref-

erence circuit is powered down. The voltage reference is

trimmed to 1.30 V at room temperature.

A temperature proportional voltage is also produced in this

block for use in temperature sensing.

Figure 29-1. Voltage Reference Schematic

29.2

Register Definitions

The following register is associated with the Internal Voltage Reference. The Internal Voltage Reference is trimmed for gain

and temperature coefficient using the BDG_TR register. The register description below has an associated register table

showing the bit structure. The bits that are grayed out in the table are reserved bits and are not detailed in the register

description that follows. Reserved bits should always be written with a value of ‘0’.

29.2.1

BDG_TR Register

The Bandgap Trim Register (BDG_TR) is used to adjust the

bandgap and add an RC filter to AGND.

Depending on how many analog columns your PSoC device

has (see the Cols. column in the register table above), only

certain bits are accessible to be read or written.

Bit 6: AGNDBYP.

When set, this bit adds an RC filter to

AGND. (R is an internal 8.1K resistor and C is external to

the PSoC device on P2[4].)

Bits 5 and 4: TC[1:0].

These bits are for setting the tem-

perature coefficient inside the bandgap voltage generator.

10b is the design center for ‘0’ TC.

It is strongly recommended that the user not alter the

value of these bits.

Bits 3 to 0: V[3:0].

These bits are for setting the gain in the

reference buffer. Sixteen steps of 4 mV are available. 1000b

is the design center for 1.30 V.

It is strongly recommended that the user not alter the

value of these bits.

For additional information, refer to the

V

BG

+

-

S + H

V

REF

Add.

Name

Cols.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

1,EAh

4, 2

AGNDBYP

TC[1:0]

V[3:0]

RW : 00

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...