CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

77

General Purpose I/O (GPIO)

6.2.4

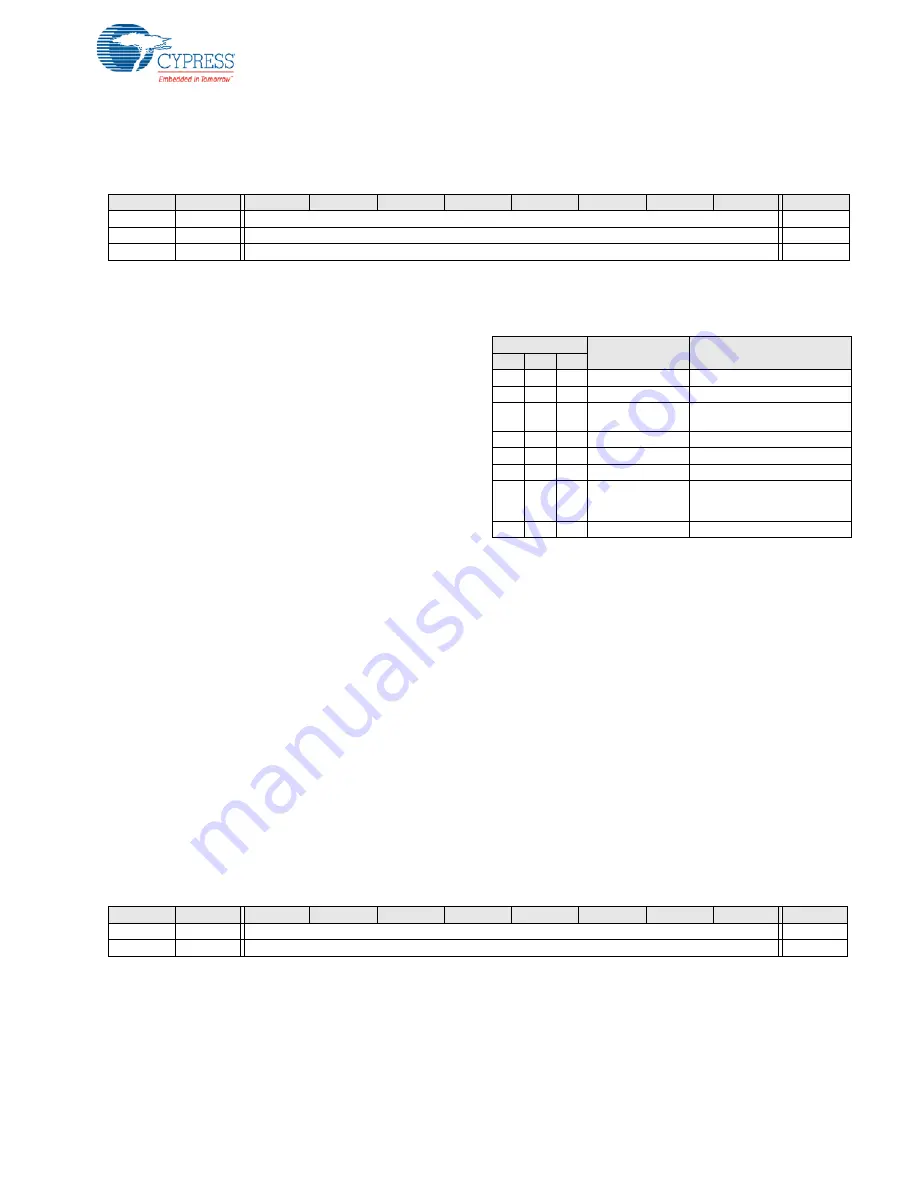

PRTxDMx Registers

The Port Drive Mode Bit Registers (PRTxDMx) are used to

specify the Drive mode for GPIO pins.

Bits 7 to 0: Drive Mode x[7:0].

In the PRTxDMx registers

there are eight possible drive modes for each port pin. Three

mode bits are required to select one of these modes, and

these three bits are spread into three different registers

(PRTxDM0, PRTxDM1, and PRTxDM2). The bit position of

the effected port pin (for example, Pin[2] in Port 0) is the

same as the bit position of each of the three drive mode reg-

ister bits that control the Drive mode for that pin (for exam-

ple, bit[2] in PRT0DM0, bit[2] in PRT0DM1, and bit[2] in

PRT0DM2). The three bits from the three registers are

treated as a group. These are referred to as DM2, DM1, and

DM0, or together as DM[2:0]. Drive modes are shown in

.

For analog I/O, the Drive mode should be set to one of the

High-Z modes, either 010b or 110b. The 110b mode has the

advantage that the block’s digital input buffer is disabled, so

no

current flows even when the analog input is not

close to either power rail. When digital inputs are needed on

the same pin as analog inputs, the 010b Drive mode should

be used. If the 110b Drive mode is used, the pin will always

be read as a zero by the CPU and the pin will not be able to

generate a useful interrupt. (It is not strictly required that a

High-Z mode be selected for analog operation.)

For global input modes, the Drive mode must be set to

010b.

The GPIO provides a default Drive mode of high imped-

ance, analog (High-Z). This is achieved by forcing the reset

state of all PRTxDM1 and PRTxDM2 registers to FFh.

The resistive drive modes place a

in series with

the output, for low outputs (mode 000b) or high outputs

(mode 011b). Strong Drive mode 001b gives the fastest

edges at high DC drive strength. Mode 101b gives the same

drive strength but with slower edges. The open-drain modes

(100b and 111b) also use the slower edge rate drive. These

modes enable open-drain functions such as I

2

C mode 111b

(although the slow edge rate is not slow enough to meet the

I

2

C fast mode specification).

For additional information, refer to the

, the

, and the

6.2.5

PRTxICx Registers

The Port Interrupt Control Registers (PRTxIC1 and

PRTxIC0) are used to specify the Interrupt mode for GPIO

pins.

Bits 7 to 0: Interrupt Control x[7:0].

In the PRTxICx reg-

isters, the Interrupt mode for the pin is determined by bits in

these two registers. These are referred to as IC1 and IC0, or

together as IC[1:0].

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

0,xxh

Drive Mode 2[7:0]

RW : FFh

1,xxh

Drive Mode 0[7:0]

RW : 00

1,xxh

Drive Mode 1[7:0]

RW : FFh

LEGEND

xx An “x” after the comma in the address field indicates that there are multiple instances of the register. For an expanded address listing of these registers,

refer to the

“Core Register Summary” on page 36

Table 6-1. Pin Drive Modes

Drive Modes

Pin State

Description

DM2 DM1 DM0

0

0

0

Resistive pull down

Strong high, resistive low

0

0

1

Strong drive

Strong high, strong low

0

1

0

High impedance

High-Z high and low, digital input

enabled

0

1

1

Resistive pull up

Resistive high, strong low

1

0

0

Open drain high

Slow strong high, High-Z low

1

0

1

Slow strong drive

Slow strong high, slow strong low

1

1

0

High impedance,

analog (

reset state

)

High-Z high and low, digital input

disabled (for zero power) (

reset

state

)

1

1

1

Open drain low

Slow strong low, High-Z high

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

1,xxh

Interrupt Control 0[7:0]

RW : 00

1,xxh

Interrupt Control 1[7:0]

RW : 00

LEGEND

xx An “x” after the comma in the address field indicates that there are multiple instances of the register. For an expanded address listing of these registers,

refer to the

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...