Epson Research and Development

Page 39

Vancouver Design Center

Programming Notes and Examples

S1D13704

Issue Date: 01/02/12

X26A-G-002-03

7.4 Registers

This section describes the registers used to set SwivelView mode operation.

The start address registers must be set for SwivelView mode. In SwivelView mode the

offset contained in the start address points to a byte.

The line byte count register informs the S1D13704 of the stride, in bytes, between two

consecutive lines of display in SwivelView mode. The Line Byte Count register only

affects SwivelView mode operation. The contents of this register are ignored when the

S1D13704 is in landscape display mode.

The SwivelView mode register contains several items for SwivelView mode support.

The first is the SwivelView Mode Enable bit. When this bit is “0” the S1D13704 is in

landscape mode and the remainder of the settings in this register as well as the Line Byte

Count in REG[1Ch] are ignored. When this bit is a “1” SwivelView mode is enabled.

There are two SwivelView mode display schemes available. The SwivelView mode select

bit selects between the “Default Mode” and the "Alternate Mode”. The default mode offers

the lowest power consumption with some display mode limitations. The alternate mode

uses more power but offers greater display flexibility.

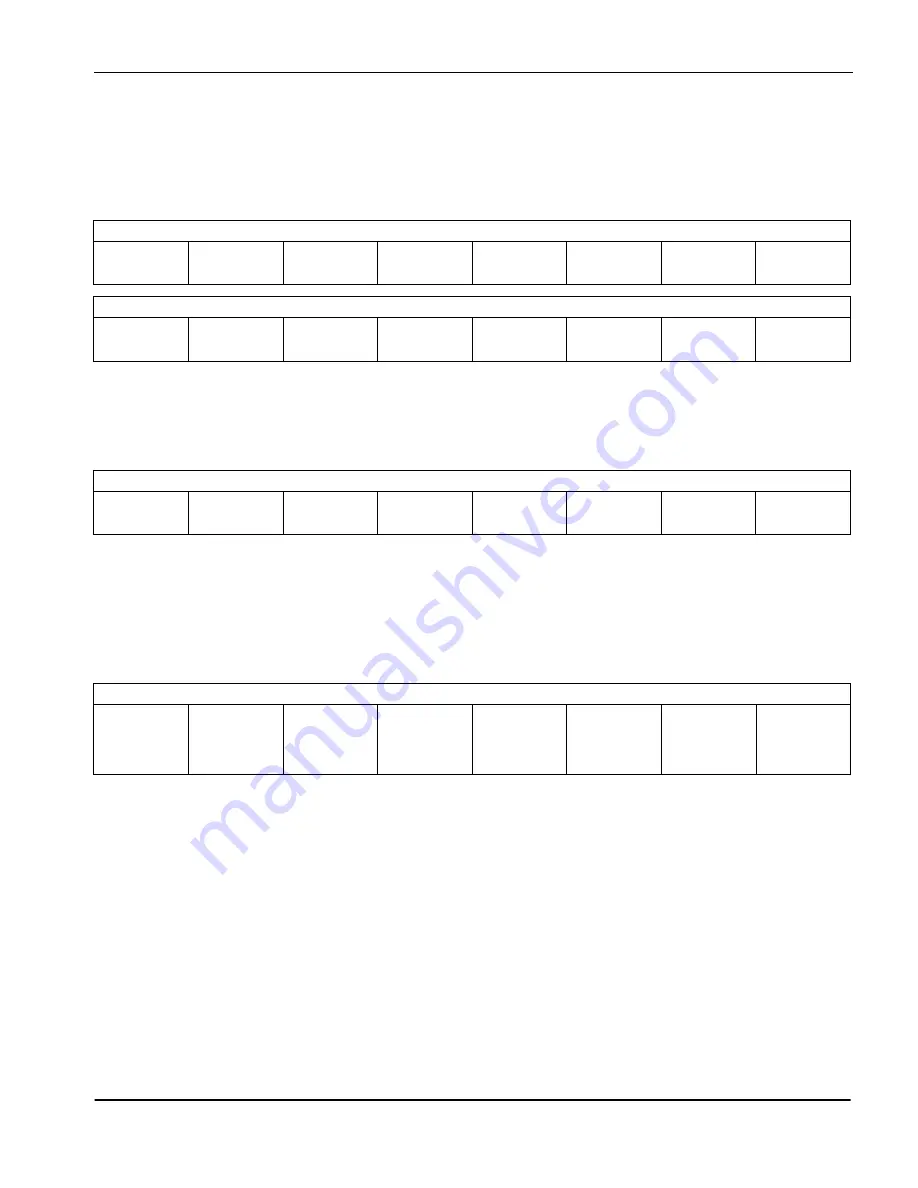

REG[0Ch] Screen 1 Start Word Address LSB

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

REG[0Dh] Screen 1 Start Word Address MSB

reserved

bit 14

bit 13

bit 12

bit 11

bit 10

bit 9

bit 8

REG[1Ch] Line Byte Count Register

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

REG[1Bh] SwivelView Mode Register

SwivelView

Mode Enable

SwivelView

Mode Select

n/a

n/a

n/a

reserved

SwivelView

Mode Pixel

Clock Select

Bit 1

SwivelView

Mode Pixel

Clock Select

Bit 0

*