TPMC533 User Manual Issue 1.0.1

Page 60 of 107

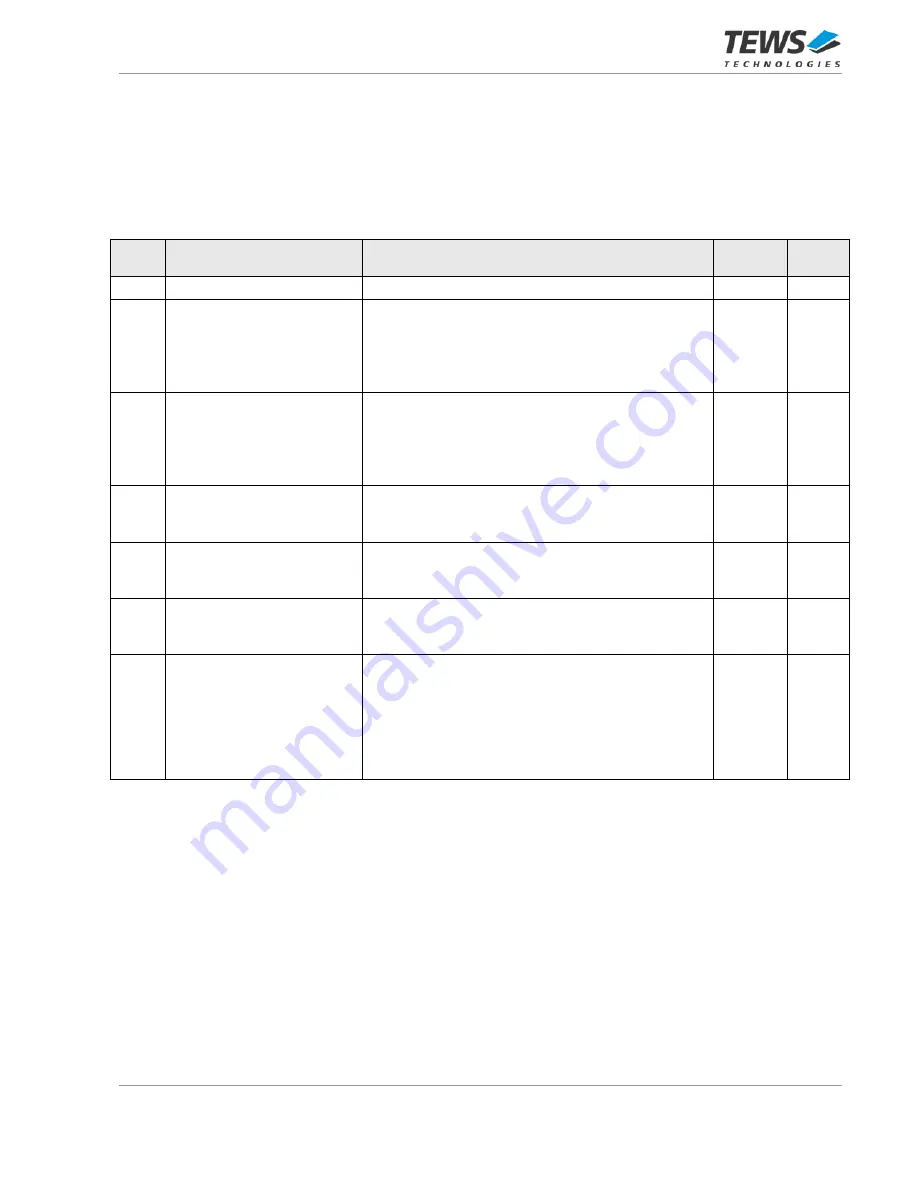

3.2.1.9 Interrupt Registers

3.2.1.9.1

Interrupt Enable Register (0x36C)

For an interrupt status bit to be set, the interrupt must be enabled prior to the interrupt event.

Disabling an interrupt clears the appropriate interrupt status bit.

Bit

Symbol

Description

Access

Reset

Value

31:30

-

Reserved

-

-

29

FRAME_TIMER_IRQ_ENA

Enable IRQ at Frame Timer event

0: disabled

1: enabled

If enabled, an interrupt will be generated when the

Frame Timer has expired.

R/W

0

28

FRAME_TRIG_ENA

Enable IRQ at Frame Trigger event

0: disabled

1: enabled

If enabled, an interrupt will be generated when the

Frame Trigger signal is detected.

R/W

0

27

ADC4_DONE_ENA

Enable IRQ after ADC4 Conversion is done

Refer to the Enable IRQ after ADC1 Conversion is done

bit for description.

R/W

0

26

ADC3_DONE_ENA

Enable IRQ after ADC3 Conversion is done

Refer to the Enable IRQ after ADC1 Conversion is done

bit for description.

R/W

0

25

ADC2_DONE_ENA

Enable IRQ after ADC2 Conversion is done

Refer to the Enable IRQ after ADC1 Conversion is done

bit for description.

R/W

0

24

ADC1_DONE_ENA

Enable IRQ after ADC1 Conversion is done

0: disabled

1: enabled

If enabled, in Manual Mode an interrupt will be

generated after a conversion of ADC1 is finished and

ADC Data is available (ADC1_BUSY changes from '1'

to '0' in Global ADC Status Register).

R/W

0