TPMC533 User Manual Issue 1.0.1

Page 73 of 107

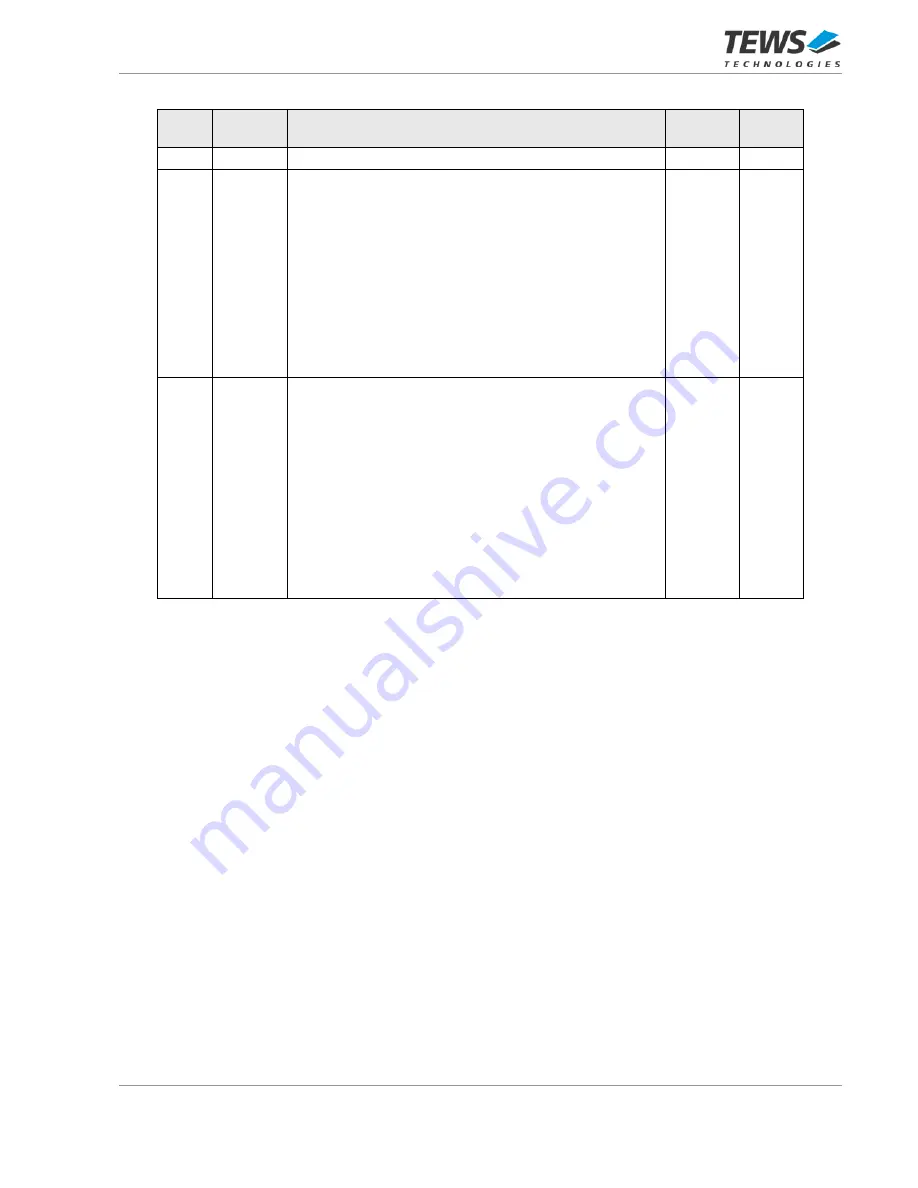

3.2.1.10.4 Correction Data EEPROM Control/Status Register (0x3A4)

Bit

Symbol

Description

Access

Reset

Value

31:17

-

Reserved

-

-

16

EEBSY

Read-only Activity Status of the on-board Correction Data

EEPROM

0: Correction Data loading is done

1: Correction Data loading in progress

After power-up or PCI reset, the content of the Correction

Data EEPROM is automatically copied to the Correction

Data ROM. During this process, the EEBSY is set.

The EEBSY bit is also set when the EELOCK nibble is

changed from 0xABCD to a different value while data is

written to (or read from) the EEPROM.

Software should check that the EEBSY bit is ‘0’ before

reading data from the Correction Data ROM space.

R

0

15:0

EELOCK

Correction Data EEPROM Lock

This nibble must be set to the value 0xABCD to allow write

accesses to the Correction Data ROM. Writes to the

Correction Data ROM are ignored while this nibble is not

0xABCD.

When the value of this nibble is changed from 0xABCD to a

different value, an automatic EEPROM update procedure is

started: The content of the Correction Data ROM is stored in

the on-board Correction Data EEPROM, and is immediately

read back to the Correction Data ROM.

The EEBSY bit is set during this procedure.

Before setting the EELOCK nibble to 0xABCD, software

should check that the EEBSY bit is clear.

R/W

0x0000

Table 3-72: Correction Data EEPROM Control/Status Register