TPMC533 User Manual Issue 1.0.1

Page 63 of 107

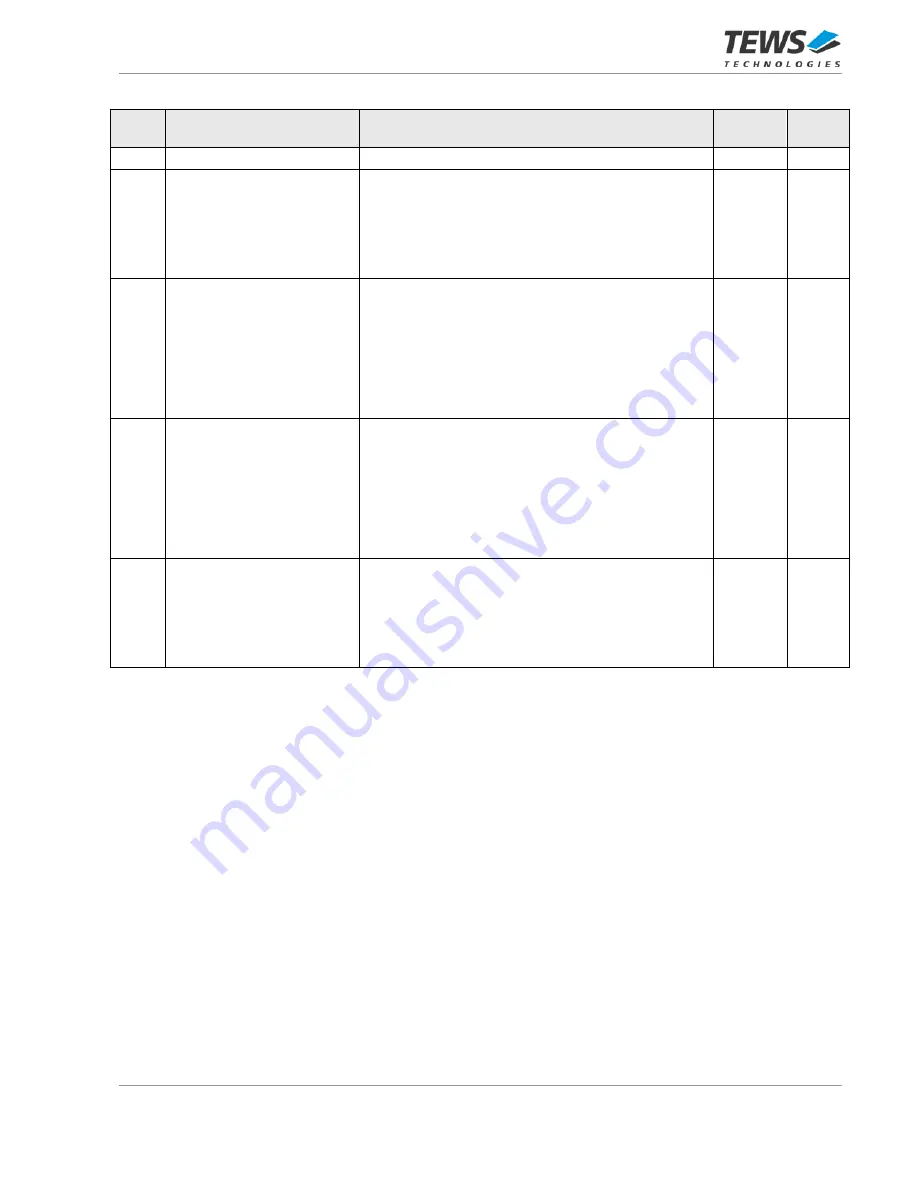

3.2.1.9.2

Error Interrupt Enable Register (0x370)

Bit

Symbol

Description

Access

Reset

Value

31:28

-

Reserved

-

-

27

IU_FRAME_ERR_IRQ_ENA

Enable IRQ at ADC Sequencer Input Unit Frame Error

0: disabled

1: enabled

If enabled, an interrupt is asserted if a Frame Trigger

event occurs, but the configured Number of

Conversions has not been processed so far.

R/W

0

26

CONV_ERR_IRQ_ENA

Enable IRQ at ADC Sequencer Input Unit Conversion

Error

0: disabled

1: enabled

If enabled, an interrupt is asserted when the Sequencer

Conversion Clock Source requests the next conversion,

but the ADCs are still busy performing the conversion

process of the previous conversion.

R/W

0

25

FIFO_OF_IRQ_ENA

Enable IRQ at ADC Sequencer Input Unit FIFO

Overflow Error

0: disabled

1: enabled

If enabled, an interrupt is asserted when the Input Unit

wants to write sampled values from the ADCs to the

FIFO but the FIFO is full because AD samples could not

be written to Host RAM fast enough.

R/W

0

24

WR_DMA_ERR_IRQ_ENA

Enable IRQ at ADC Sequencer DMA Error

0: disabled

1: enabled

If enabled, an interrupt is asserted when the DMA

Controller of the ADC Sequencer faces a PCI Bus

Abort.

R/W

0