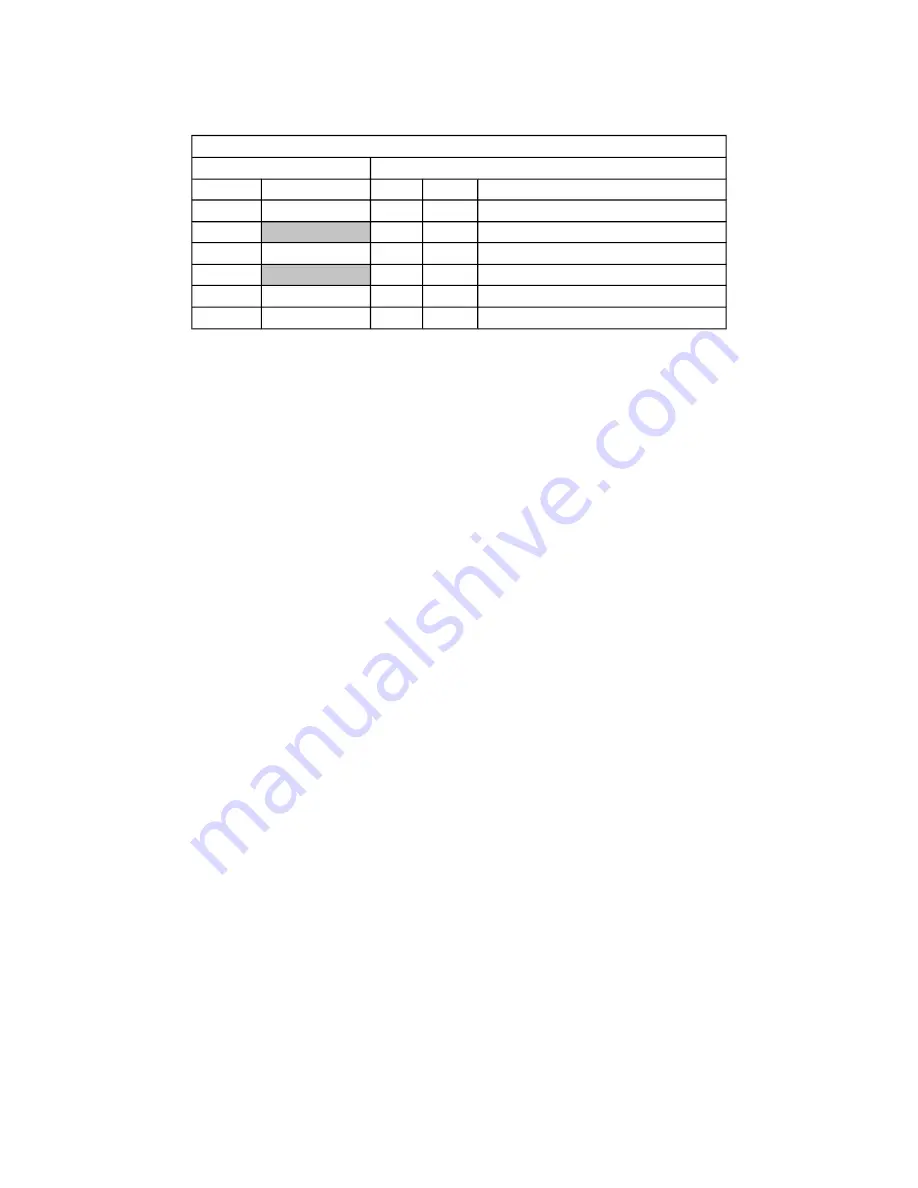

hfrosccfg: Ring Oscillator Configuration and Status (

hfrosccfg

)

Register Offset

0x0

Bits

Field Name

Attr.

Rst.

Description

[5:0]

hfroscdiv

RW

0x4

Ring Oscillator Divider Register

[15:6]

Reserved

[20:16]

hfrosctrim

RW

0x10

Ring Oscillator Trim Register

[29:21]

Reserved

30

hfroscen

RW

0x1

Ring Oscillator Enable

31

hfroscrdy

RO

X

Ring Oscillator Ready

The frequency can be adjusted in software using a 5-bit trim value in the

hfrosctrim

. The trim

value (from 0–31) adjusts which tap of the variable delay chain is fed back to the start of the

ring. A value of 0 corresponds to the longest chain and slowest frequency, while higher values

correspond to shorter chains and therefore higher frequencies.

The HFROSC oscillator output frequency can be divided by an integer between 1 and 64 giving

a frequency range of 1.125 MHz–72 MHz assuming the trim value is set to give a 72 MHz out-

put. The value of the divider is given in the

hfroscdiv

field, where the divide ratio is one greater

than the binary value held in the field (i.e.,

hfroscdiv

=0 indicates divide by 1,

hfroscdiv

=1

indicates divide by 2, etc.). The value of the divider can be changed at any time.

The HFROSC is the default clock source used for the system core at reset. After a reset, the

hfrosctrim

value is reset to 16, the middle of the adjustable range, and the divider is reset to

divide-by-5 (

hfroscdiv

=4), which gives a nominal 13.8 MHz (±50%) output frequency.

The value of

hfrosctrim

that most closely achieves an 72 MHz clock output at nominal condi-

tions (1.8 V at 25 °C) is determined by manufacturing-time calibration and is stored in on-chip

OTP storage. Upon reset, software in the processor boot sequence can write the calibrated

value into the

hfrosctrim

field, but the value can be altered at any time during operation

including when the processor is running from HFROSC.

To save power, the HFROSC can be disabled by clearing

hfroscen

. The processor must be

running from a different clock source (the PLL, external crystal, or external clock) before dis-

abling HFROSC. HFROSC can be explicitly renabled by setting

hfroscen

. HFROSC will be

automatically re-enabled at every reset.

The status bit

hfroscrdy

indicates if the oscillator is operational and ready for use as a clock

source.

External 16 MHz Crystal Oscillator (HFXOSC)

An external high-frequency 16 MHz crystal oscillator can be used to provide a precise clock

source. The crystal oscillator should have a capacitive load of ≤ 12 pF and an ESR ≤ 80 Ω.

Table 9:

hfrosccfg: Ring Oscillator Configuration and Status

Copyright © 2019, SiFive Inc. All rights reserved.

27

Summary of Contents for FE310-G002

Page 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

Page 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Page 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Page 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...