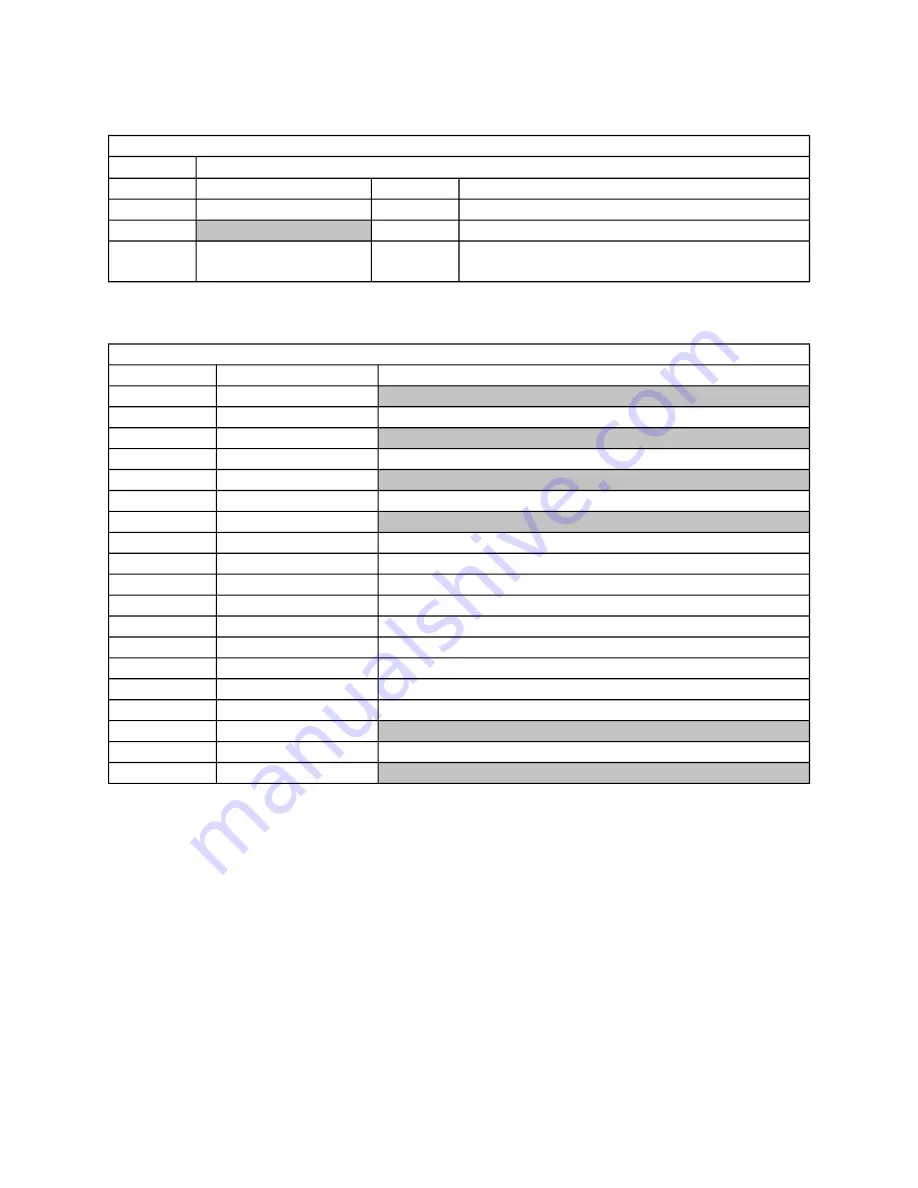

Machine Cause Register

CSR

mcause

Bits

Field Name

Attr.

Description

[9:0]

Exception Code

WLRL

A code identifying the last exception.

[30:10]

Reserved

WLRL

31

Interrupt

WARL

1 if the trap was caused by an interrupt; 0

otherwise.

Table 22:

mcause

Register

Interrupt Exception Codes

Interrupt

Exception Code

Description

1

0–2

Reserved

1

3

Machine software interrupt

1

4–6

Reserved

1

7

Machine timer interrupt

1

8–10

Reserved

1

11

Machine external interrupt

1

≥ 12

Reserved

0

0

Instruction address misaligned

0

1

Instruction access fault

0

2

Illegal instruction

0

3

Breakpoint

0

4

Load address misaligned

0

5

Load access fault

0

6

Store/AMO address misaligned

0

7

Store/AMO access fault

0

8

Environment call from U-mode

0

9–10

Reserved

0

11

Environment call from M-mode

0

≥ 12

Reserved

Table 23:

mcause

Exception Codes

Individual priorities of global interrupts are determined by the PLIC, as discussed in Chapter 10.

FE310-G002 interrupts are prioritized as follows, in decreasing order of priority:

• Machine external interrupts

• Machine software interrupts

• Machine timer interrupts

Copyright © 2019, SiFive Inc. All rights reserved.

40

Summary of Contents for FE310-G002

Page 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

Page 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Page 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Page 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...