11 16-BIT TIMER (T16)

108

EPSON

S1C17001 TECHNICAL MANUAL

11.2 16-bit Timer Operating Modes

The 16-bit timer has the following three operating modes:

1. Internal clock mode (Normal timer counting internal clock)

2. External clock mode (Functions as event counter)

3. Pulse width measurement mode (Counts external input pulse width using internal clock)

The operating mode is selected using CKSL[1:0] (D[9:8]/T16_CTL

x

register).

∗

CKSL[1:0]

: Input Clock and Pulse Width Count Mode Select Bits in the 16-bit Timer Ch.

x

Control (T16_CTL

x

)

Register (D[9:8]/0x4226/0x4246/0x4266)

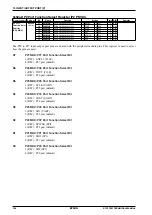

Table 11.2.1: Operating mode selection

CKSL[1:0]

Operating mode

0x3

Reserved

0x2

Pulse width measurement mode

0x1

External clock mode

0x0

Internal clock mode

(Default: 0x0)

11.2.1 Internal Clock Mode

Internal clock mode uses the prescaler output clock as the count clock.

The timer counts down from the initial value set in the reload data register and outputs an underflow signal when

the counter underflows. The underflow signal is used to generate an interrupt and an internal serial interface clock.

The time until underflow occurs can be finely programmed by selecting the prescaler clock and initial counter

value, making it useful for serial transfer clock generation and sporadic time measurement.

Count clock selection

The count clock is selected by the DF[3:0] (D[3:0]/T16_CLK

x

register) from the 15 types generated by the pr-

escaler dividing the PCLK clock into 1/1 to 1/16 K divisions.

∗

DF[3:0]

:

Timer Input Clock Select Bits in the 16-bit Timer Ch.

x

Input Clock Select (T16_CLK

x

) Register

(D[3:0]/0x4220/0x4240/0x4260)

Table 11.2.1.1: Count clock selection

DF[3:0]

Prescaler output clock

DF[3:0]

Prescaler output clock

0xf

Reserved

0x7

PCLK-1/128

0xe

PCLK-1/16384

0x6

PCLK-1/64

0xd

PCLK-1/8192

0x5

PCLK-1/32

0xc

PCLK-1/4096

0x4

PCLK-1/16

0xb

PCLK-1/2048

0x3

PCLK-1/8

0xa

PCLK-1/1024

0x2

PCLK-1/4

0x9

PCLK-1/512

0x1

PCLK-1/2

0x8

PCLK-1/256

0x0

PCLK-1/1

(Default: 0x0)

Note: • The prescaler must run before operating the 16-bit timer in internal clock mode.

• Make sure the 16-bit timer count is halted before changing count clock settings.

For detailed information on the prescaler control, see “9 Prescaler (PSC).”

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...