13 PWM & CAPTURE TIMER (T16E)

148

EPSON

S1C17001 TECHNICAL MANUAL

Clock output Fine mode settings

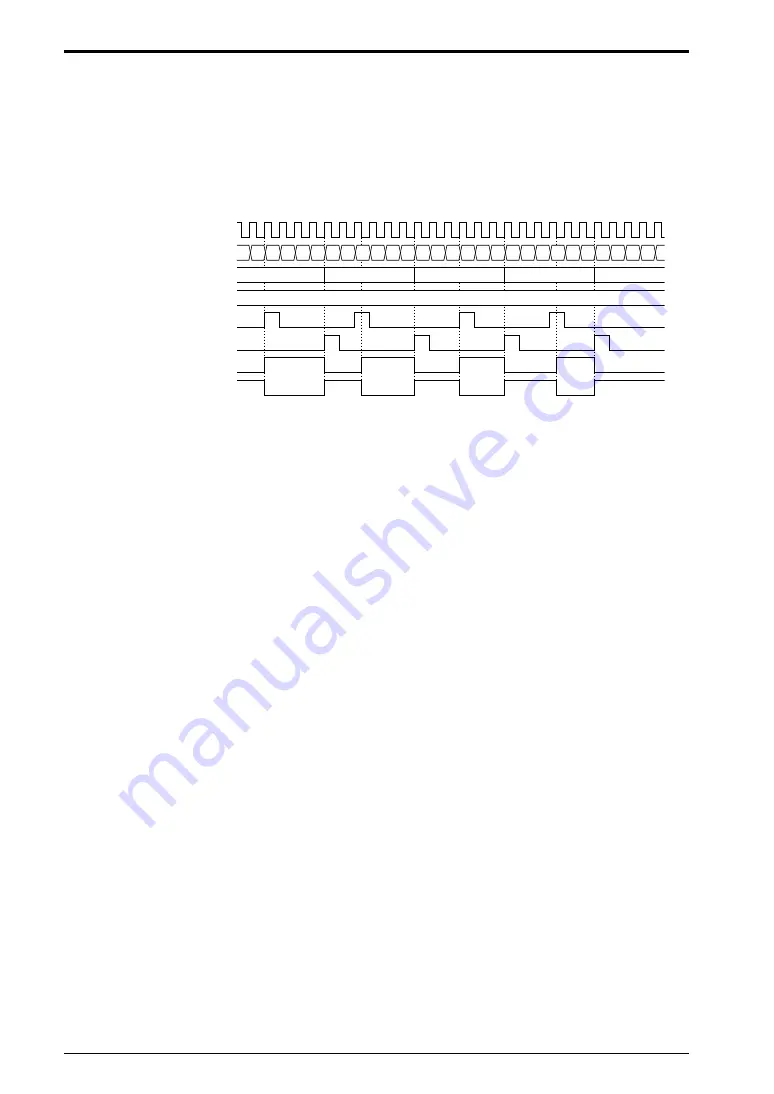

With the default settings, the clock output changes at the input clock rise-up if the counter value matches the

compare data A.

If the counter data register T16ETC[14:0] matches the compare data A register T16ECA0[15:1], the Fine mode

clock output changes in accordance with the compare data A bit 0 (T16ECA0) value.

When T16ECA0 is 0: Changes at input clock rise-up.

When T16ECA0 is 1: Changes at half-cycle delayed input clock drop-off.

Input clock

Counter value

T16E_CA

T16E_CB

Compare A signal

Compare B signal

TOUT output (INVOUT = 0)

TOUT output (INVOUT = 1)

0

2

3

4

5

6

1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 3

5

Figure 13.6.3: Fine mode clock output

The output duty can thus be adjusted in Fine mode in input clock half-cycle steps. Note that a pulse will be out-

put with an input clock 1-cycle width when compare data A = 0 (same as for default). The maximum value for

compare data B in Fine mode is 2

15

– 1 = 32,767, and the compare data A range will be 0 to (2 x compare data

B - 1).

Fine mode is set by SELFM (D6/T16E_CTL register).

∗

SELFM

: Fine Mode Select Bit in the PWM Timer Control (T16E_CTL) Register (D6/0x5306)

Writing 1 to SELFM sets Fine mode. Fine mode is disabled after initial resetting.

Precautions

(1) Compare data should be set with A

≥

0 and B

≥

1 when using the timer output. The minimum settings are A

= 0 and B = 1, and the timer output cycle is half the input clock.

(2) Setting compare data with A > B (A > B x 2 for Fine mode) generates a compare B match signal only. It

does not generate a compare A match signal. In this case, the timer output is fixed at Low (High when IN-

VOUT = 1).

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...