6 INITERRUPT CONTROLLER

S1C17001 TECHNICAL MANUAL

EPSON

33

6.3.4 Processing for Multiple Interrupts

The ITC ITC_ELV

x

and ITC_ILV

x

registers (0x4306 to 0x4314) set the interrupt levels (0 to 7) for the various in-

terrupt factors.

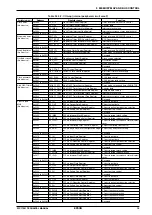

Table 6.3.4.1: Interrupt level setting bits

Vector No.

Hardware interrupt

Interrupt level setting bit

Register address

4

P0 port interrupt

EILV0[2:0] (D[2:0]/ITC_ELV0 register)

0x4306

5

P1 port interrupt

EILV1[2:0] (D[10:8]/ITC_ELV0 register)

0x4306

6

Stopwatch timer interrupt

EILV2[2:0] (D[2:0]/ITC_ELV1 register)

0x4308

7

Clock timer interrupt

EILV3[2:0] (D[10:8]/ITC_ELV1 register)

0x4308

8

8-bit OSC1 timer interrupt

EILV4[2:0] (D[2:0]/ITC_ELV2 register)

0x430a

11

PWM & capture timer interrupt

EILV7[2:0] (D[10:8]/ITC_ELV3 register)

0x430c

12

8-bit timer interrupt

IILV0[2:0] (D[2:0]/ITC_ILV0 register)

0x430e

13

16-bit timer Ch.0 interrupt

IILV1[2:0] (D[10:8]/ITC_ILV0 register)

0x430e

14

16-bit timer Ch.1 interrupt

IILV2[2:0] (D[2:0]/ITC_ILV1 register)

0x4310

15

16-bit timer Ch.2 interrupt

IILV3[2:0] (D[10:8]/ITC_ILV1 register)

0x4310

16

UART interrupt

IILV4[2:0] (D[2:0]/ITC_ILV2 register)

0x4312

17

Remote controller interrupt

IILV5[2:0] (D[10:8]/ITC_ILV2 register)

0x4312

18

SPI interrupt

IILV6[2:0] (D[2:0]/ITC_ILV3 register)

0x4314

19

I

2

C interrupt

IILV7[2:0] (D[10:8]/ITC_ILV3 register)

0x4314

The interrupt level can range from 0 to 7.

The interrupt level set is issued to the S1C17 core at the same time as an interrupt request from the ITC. This inter-

rupt level is used in the S1C17 core to prohibit subsequent interrupts with the same or lower levels (refer to Section

6.3.6).

Initial resets reset all interrupt levels to 0. The S1C17 core rejects interrupt requests if the interrupt level is 0.

The ITC uses the interrupt level when multiple interrupt factors occur simultaneously.

If multiple interrupts occur at the same time permitted by the interrupt enable bit, the ITC sends the interrupt re-

quest with the highest level set by the ITC_ELV

x

and ITC_ILV

x

registers to the S1C17 core.

If multiple interrupt factors with the same interrupt level occur simultaneously, the interrupt with the lowest vector

number is processed first. The other interrupts are held until all have been accepted by the S1C17 core in descend-

ing order of priority.

If an interrupt factor of higher priority occurs while the ITC outputs an interrupt request signal to the S1C17 core

(before acceptance by the S1C17 core), the ITC alters the vector number and interrupt level signal to the setting de-

tails of the most recent interrupt. The immediately preceding interrupt is held.

Summary of Contents for S1C17001

Page 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Page 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Page 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...