IDT SMBus Interfaces

Slave SMBus Interface

PES12N3 User Manual

7 - 12

June 7, 2006

Notes

Serial EEPROM Read or Write Operation

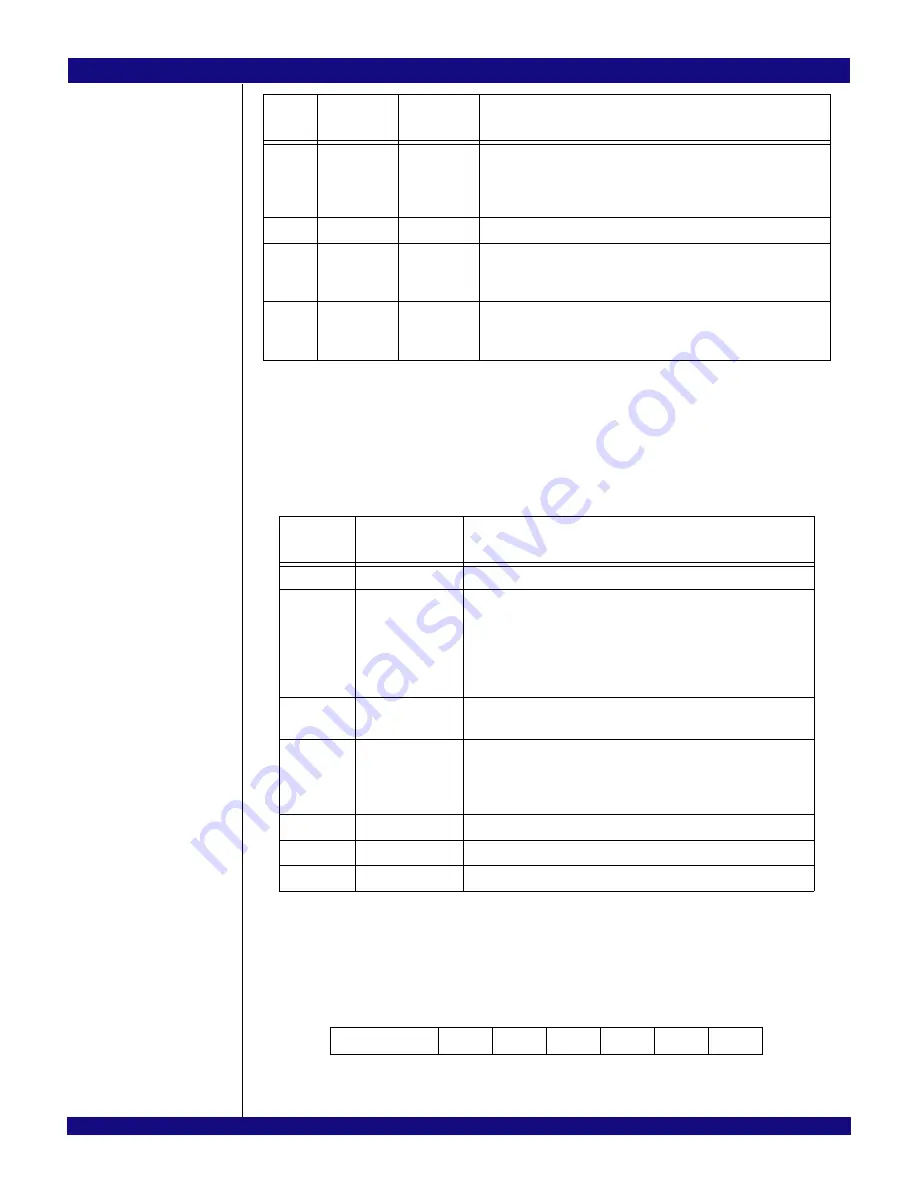

Table 7.11 indicates the sequence of data as it is presented on the slave SMBus following the byte

address of the Slave SMBus interface.

The format of the CMD field is shown in Figure 7.7 and described in Table 7.12

Figure 7.7 Serial EEPROM Read or Write CMD Field Format

4

OP

Read/Write

CSR Operation. This field encodes the CSR operation to be per-

formed.

0 - CSR write

1 - CSR read

5

0

0

Reserved. Must be zero

6

RERR

Read-Only

and Clear

Read Error. This bit is set if the last CSR read SMBus transaction was

not claimed by a device. Success indicates that the transaction was

claimed and not that the operation completed without error.

7

WERR

Read-Only

and Clear

Write Error. This bit is set if the last CSR write SMBus transaction was

not claimed by a device. Success indicates that the transaction was

claimed and not that the operation completed without error.

Byte

Position

Field

Name

Description

0

CCODE

Command Code. Slave Command Code field described in Table 7.8.

1

BYTCNT

Byte Count. The byte count field is only transmitted for block type

SMBus transactions. SMBus word and byte accesses do not contain

this field. The byte count field indicates the number of bytes following

the byte count field when performing a write or setting up for a read.

The byte count field is also used when returning data to indicate the

number of following bytes (including status).

2

CMD

Command. This field contains information related to the serial

EEPROM transaction

3

EEADDR

Serial EEPROM Address. This field specifies the address of the

Serial EEPROM on the Master SMBus when the USA bit is set in the

CMD field. Bit zero must be zero and thus the 7-bit address must be

left-justified.

4

ADDRL

Address Low. Lower 8-bits of the Serial EEPROM byte to access.

5

ADDRU

Address Upper. Upper 8-bits of the Serial EEPROM byte to access.

6

DATA

Data. Serial EEPROM value read or to be written.

Table 7.11 Serial EEPROM Read or Write Operation Byte Sequence

Bit

Field

Name

Type

Description

Table 7.10 CSR Register Read or Write CMD Field Description (Part 2 of 2)

Bit

6

Bit

7

Bit

0

Bit

1

Bit

2

Bit

3

Bit

4

Bit

5

OP

USA

0

NAERR

LAERR

OTHERERR

0

Summary of Contents for 89HPES12N3

Page 10: ...IDT Table of Contents PES12N3 User Manual iv June 7 2006 Notes...

Page 14: ...IDT List of Figures PES12N3 User Manual viii June 7 2006 Notes...

Page 36: ...IDT Clocking Reset and Initialization Reset PES12N3 User Manual 2 8 June 7 2006 Notes...

Page 40: ...IDT Link Operation Slot Power Limit Support PES12N3 User Manual 3 4 June 7 2006 Notes...

Page 50: ...IDT Switch Operation Switch Core Errors PES12N3 User Manual 4 10 June 7 2006 Notes...

Page 54: ...IDT Power Management Active State Power Management PES12N3 User Manual 5 4 June 7 2006 Notes...

Page 62: ...IDT Hot Plug and Hot Swap Hot Swap PES12N3 User Manual 6 8 June 7 2006 Notes...

Page 78: ...IDT SMBus Interfaces Slave SMBus Interface PES12N3 User Manual 7 16 June 7 2006 Notes...

Page 148: ...IDT Test and Debug SerDes Test Clock PES12N3 User Manual 10 6 June 7 2006...

Page 158: ...IDT JTAG Boundary Scan Usage Considerations PES12N3 User Manual 11 10 June 7 2006 Notes...