29-12

MC9328MX1 Reference Manual

MOTOROLA

I

2

C Module

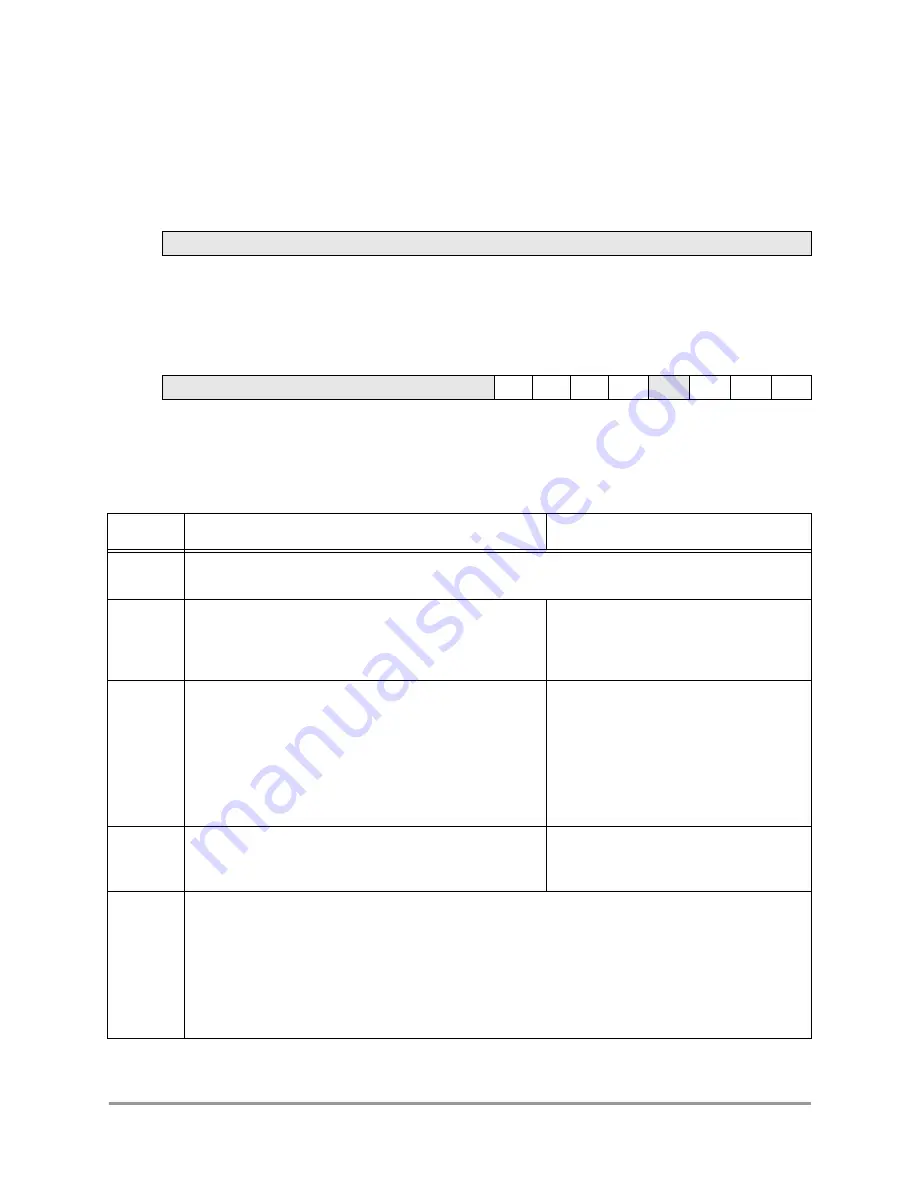

29.6.4 I

2

C Status Register

The I

2

C Status Register (I2SR) indicates transaction direction and status.

I2SR

I

2

C Status Register

Addr

0x0021700C

BIT

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

TYPE

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0000

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ICF

IAAS

IBB

IAL

SRW

IIF

RXAK

TYPE

r

r

r

r

r

r

r

r

r

r

r

rw

r

r

rw

r

RESET

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0x0081

Table 29-7. I2SR Register Description

Name

Description

Settings

Reserved

Bits 31–8

Reserved—These bits are reserved and should read 0.

ICF

Bit 7

Data Transfer

—Indicates data transfer condition. ICF is

cleared while one byte of data is transferred.

0 = Transfer in progress

1 = Transfer complete (set at the falling

edge of the ninth clock of a byte

transfer)

IAAS

Bit 6

I

2

C

Addressed As a Slave

—Indicates that the device

slave address matches the address sent on the data line.

When the I

2

C Enable (IIEN) bit in the I2CR Register is set,

an interrupt is generated to the ARM9 core when this

match occurs. The ARM9 core must check the Slave

Read/Write (SRW) bit and set the Transmit/Receive Mode

Select (MTX) bit of the I2CR Register accordingly. Writing

to the I2CR Register clears this bit.

0 = Not addressed

1 = Addressed as a slave (set when the

MC9328MX1 slave address in the

IADR Register matches the calling

address)

IBB

Bit 5

I

2

C

Bus Busy

—Indicates the status of the bus. When a

STOP signal is detected, IBB is cleared, and when a

START signal is detected, IBB is set.

0 = Bus is idle

1 = Bus is busy

IAL

Bit 4

Arbitration Lost

—Indicates that this device will not operate as bus master. IAL cleared by writing 0 to

it, and is set by the hardware in the following circumstances:

•

SDA samples low when the master drives high during an address or data-transmit cycle

•

SDA samples low when the master drives high during the acknowledge bit of a data-receive

cycle

•

A START is attempted when the bus is busy

•

A repeated START is requested in slave mode

•

A STOP condition is detected when the master did not request it

Summary of Contents for DragonBall MC9328MX1

Page 68: ...1 12 MC9328MX1 Reference Manual MOTOROLA Introduction ...

Page 86: ...2 18 MC9328MX1 Reference Manual MOTOROLA Signal Descriptions and Pin Assignments ...

Page 116: ...3 30 MC9328MX1 Reference Manual MOTOROLA Memory Map ...

Page 126: ...4 10 MC9328MX1 Reference Manual MOTOROLA ARM920T Processor ...

Page 160: ...8 8 MC9328MX1 Reference Manual MOTOROLA System Control ...

Page 272: ...13 32 MC9328MX1 Reference Manual MOTOROLA DMA Controller ...

Page 281: ...Programming Model MOTOROLA Watchdog Timer Module 14 9 ...

Page 282: ...14 10 MC9328MX1 Reference Manual MOTOROLA Watchdog Timer Module ...

Page 300: ...15 18 MC9328MX1 Reference Manual MOTOROLA Analog Signal Processor ASP ...

Page 438: ...18 16 MC9328MX1 Reference Manual MOTOROLA Serial Peripheral Interface Modules SPI 1 and SPI 2 ...

Page 478: ...19 40 MC9328MX1 Reference Manual MOTOROLA LCD Controller ...

Page 574: ...21 32 MC9328MX1 Reference Manual MOTOROLA Memory Stick Host Controller MSHC Module ...

Page 598: ...23 16 MC9328MX1 Reference Manual MOTOROLA Real Time Clock RTC ...

Page 670: ...24 72 MC9328MX1 Reference Manual MOTOROLA SDRAM Memory Controller ...

Page 726: ...25 56 MC9328MX1 Reference Manual MOTOROLA SmartCard Interface Module SIM ...

Page 736: ...26 10 MC9328MX1 Reference Manual MOTOROLA General Purpose Timers ...

Page 854: ...29 18 MC9328MX1 Reference Manual MOTOROLA I2C Module ...

Page 900: ...30 46 MC9328MX1 Reference Manual MOTOROLA Synchronous Serial Interface SSI ...

Page 942: ...32 26 MC9328MX1 Reference Manual MOTOROLA GPIO Module and I O Multiplexer IOMUX ...